Switching characteristics - serial audio interface – Cirrus Logic CS4348 User Manual

Page 9

9

CS4344/5/8

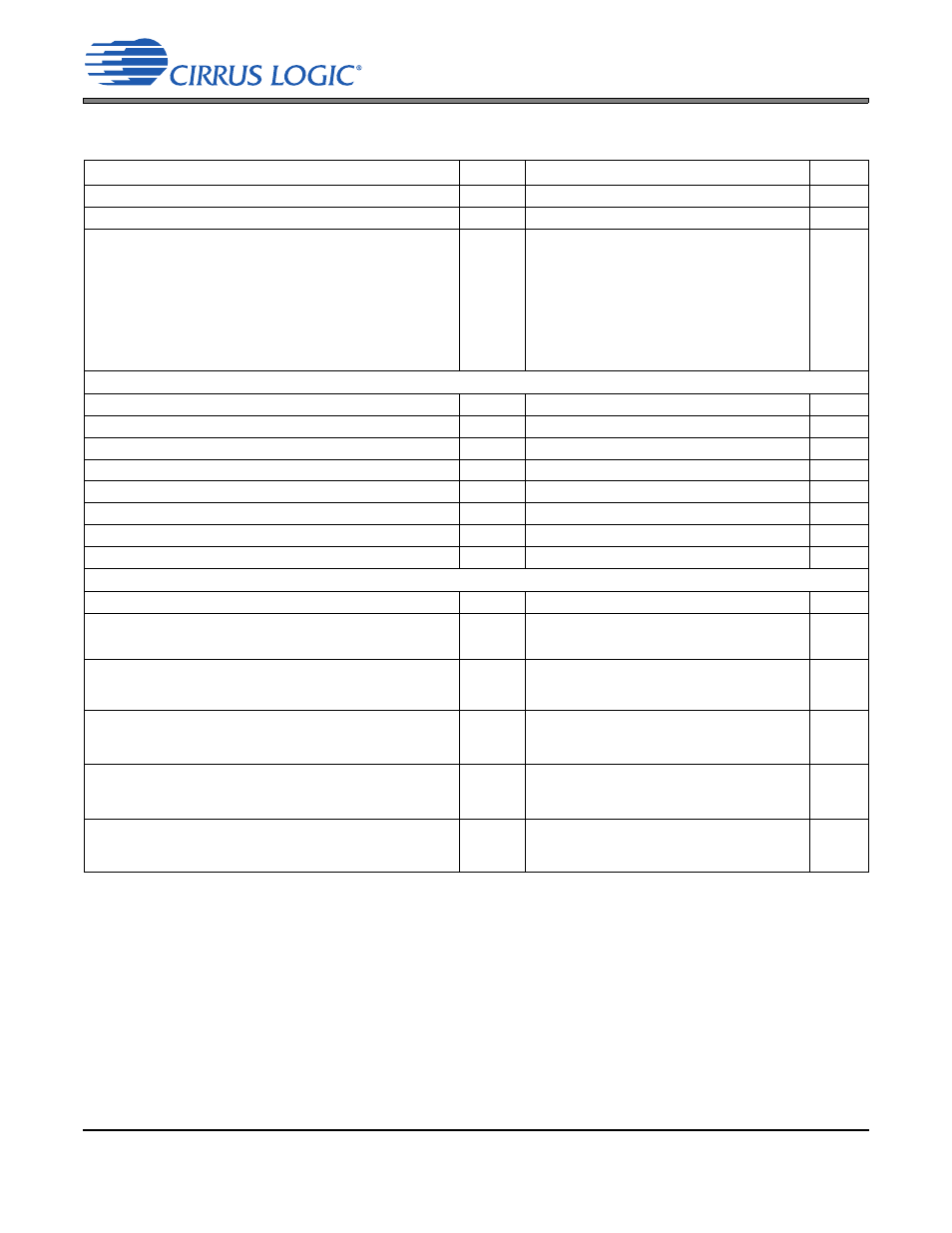

SWITCHING CHARACTERISTICS - SERIAL AUDIO INTERFACE

11. Not all sample rates are supported for all clock ratios. See

Table 1, “Common Clock Frequencies,” on

for supported ratio’s and frequencies.

12. In Internal SCLK Mode, the Duty Cycle must be 50%

1/2 MCLK Period.

13. The SCLK / LRCK ratio may be either 32, 48, 64, or 72. This ratio depends on part type and MC-

LK/LRCK ratio. (See

Parameters

Symbol Min

Typ

Max

Units

MCLK Frequency

0.512

-

50

MHz

MCLK Duty Cycle

45

-

55

%

Input Sample Rate

All MCLK/LRCK ratios combined

256x, 384x, 1024x

256x, 384x

512x, 768x

1152x

128x, 192x

64x, 96x

128x, 192x

Fs

2

2

84

42

30

50

100

168

200

50

134

67

34

100

200

200

kHz

kHz

kHz

kHz

kHz

kHz

kHz

kHz

External SCLK Mode

LRCK Duty Cycle (External SCLK only)

45

50

55

%

SCLK Pulse Width Low

t

sclkl

20

-

-

ns

SCLK Pulse Width High

t

sclkh

20

-

-

ns

SCLK Duty Cycle

45

50

55

%

SCLK rising to LRCK edge delay

t

slrd

20

-

-

ns

SCLK rising to LRCK edge setup time

t

slrs

20

-

-

ns

SDIN valid to SCLK rising setup time

t

sdlrs

20

-

-

ns

SCLK rising to SDIN hold time

t

sdh

20

-

-

ns

Internal SCLK Mode

LRCK Duty Cycle (Internal SCLK only)

-

50

-

%

SCLK Period

t

sclkw

-

-

ns

SCLK rising to LRCK edge

t

sclkr

-

-

ns

SDIN valid to SCLK rising setup time

t

sdlrs

-

-

ns

SCLK rising to SDIN hold time

MCLK / LRCK =1152, 1024, 512, 256, 128, or 64

t

sdh

-

-

ns

SCLK rising to SDIN hold time

MCLK / LRCK = 768, 384, 192, or 96

t

sdh

-

-

ns

10

9

SCLK

----------------

tsclkw

2

------------------

10

9

512

Fs

---------------------- 10

+

10

9

512

Fs

---------------------- 15

+

10

9

384

Fs

---------------------- 15

+