Figure 11, For details – Cirrus Logic CS4348 User Manual

Page 16

16

CS4344/5/8

When changing clock ratio or sample rate, it is recommended that zero data (or near zero data) be present on

SDIN for at least 10 LRCK samples before the change is made. During the clocking change, the DAC outputs will

always be in a zero data state. If no zero audio is present at the time of switching, a slight click or pop may be

heard as the DAC output automatically goes to its zero data state.

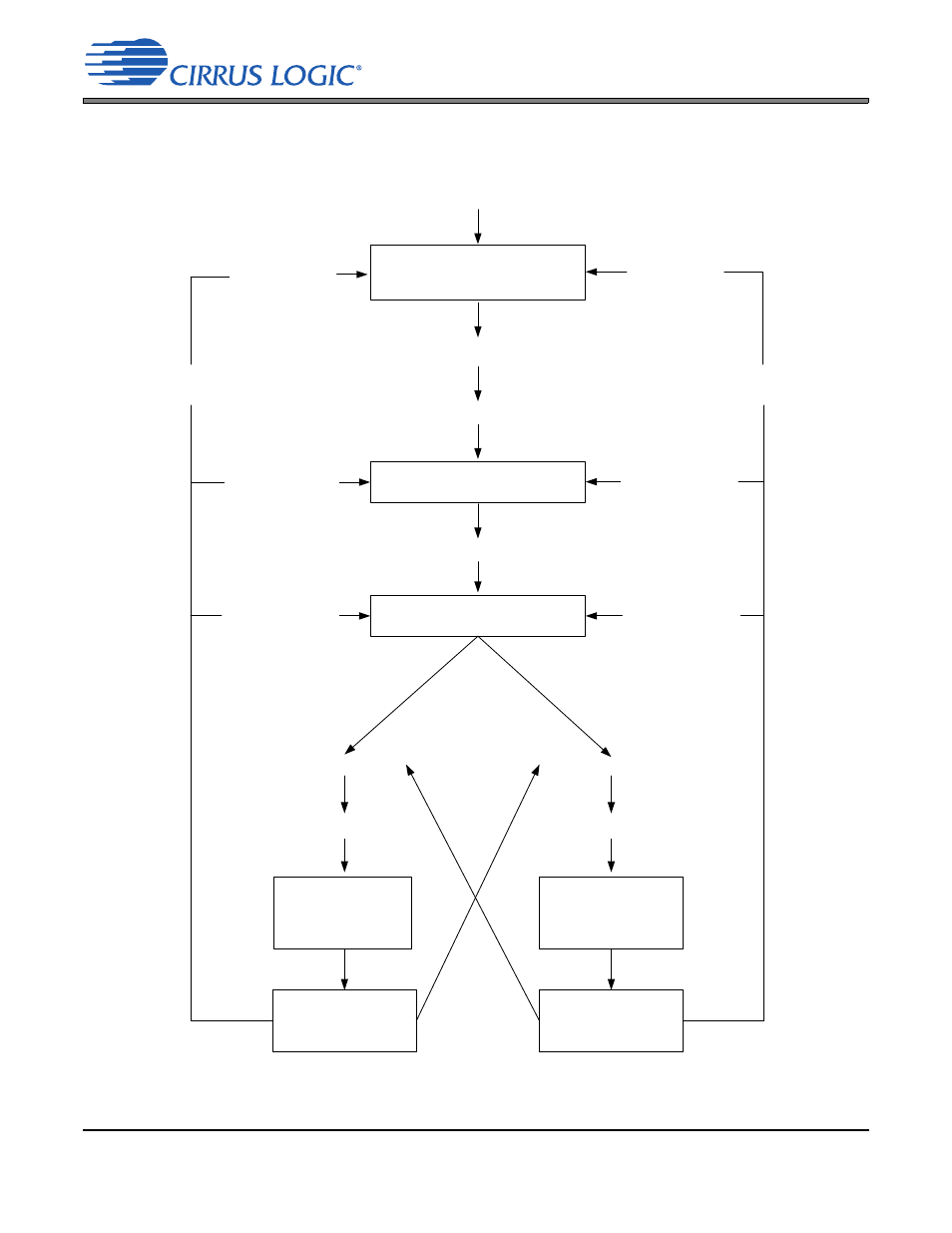

Figure 11. CS4344/5/8 Initialization and Power-down Sequence

USER: Apply Power

W ait State

USER: Apply LRCK

MCLK/LRCK Ratio Detection

USER: Applied SCLK

USER: Remove

LRCK

USER: change

MCLK/LRCK ratio

SCLK mode = internal

SCLK mode = external

Normal Operation

De-emphasis

available

Analog Output

is Generated

Normal Operation

De-emphasis

not available

Analog Output

is Generated

USER: change

MCLK/LRCK ratio

USER: Remove

MCLK

USER: Remove

LRCK

USER: Remove

MCLK

USER: Apply MCLK

Power-Down State

VQ and outputs low

VQ and outputs

ram p down

VQ and outputs

ramp down

VQ and outputs ramp up

USER: No SCLK