3 effective ratio (reff), 4 ratio configuration summary, Figure 17. ratio feature summary – Cirrus Logic CS2100-CP User Manual

Page 19: Cs2100-cp, 3 effective ratio (r

CS2100-CP

DS840F2

19

5.3.3

Effective Ratio (R

EFF

)

The Effective Ratio (R

EFF

) is an internal calculation comprised of R

UD

and the appropriate modifiers, as

previously described. R

EFF

is calculated as follows:

R

EFF

= R

UD

•

R

MOD

To simplify operation the device handles some of the ratio calculation functions automatically (such as

when the internal timing reference clock divider is set). For this reason, the Effective Ratio does not need

to be altered to account for internal dividers.

Ratio modifiers which would produce an overflow or truncation of R

EFF

should not be used; For example

if R

UD

is 1024 an R

MOD

of 8 would produce an R

EFF

value of 8192 which exceeds the 4096 limit of the

12.20 format. In all cases, the maximum and minimum allowable values for R

EFF

are dictated by the fre-

quency limits for both the input and output clocks as shown in the

“AC Electrical Characteristics” on

5.3.4

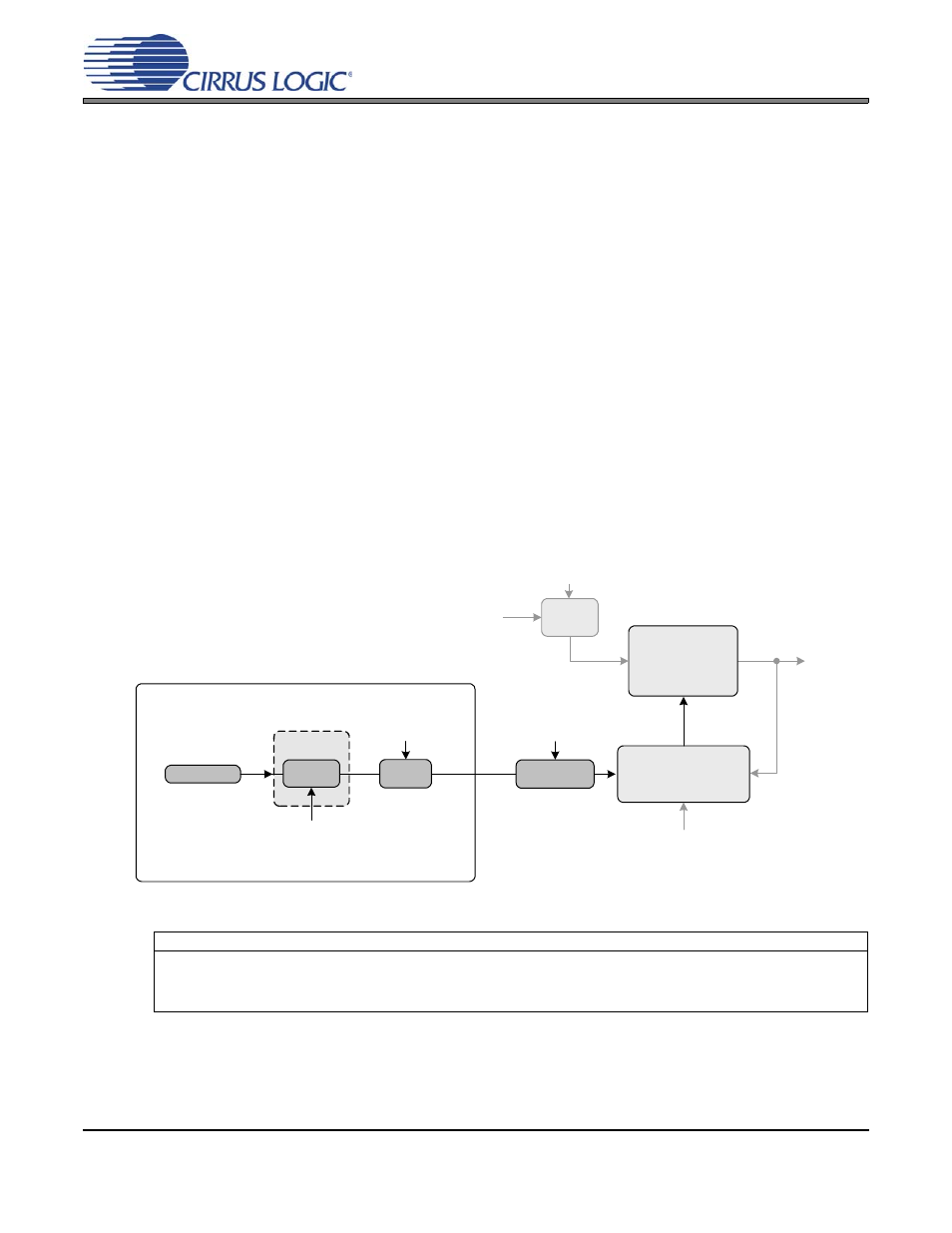

Ratio Configuration Summary

The R

UD

is the user defined ratio stored in the register space. The resolution for the R

UD

is selectable by

setting LFRatioCfg. R-Mod is applied if selected. The user defined ratio, and ratio modifier make up the

effective ratio R

EFF

, the final calculation used to determine the output to input clock ratio. The effective

ratio is then corrected for the internal dividers. The conceptual diagram in

summarizes the fea-

tures involved in the calculation of the ratio values used to generate the fractional-N value which controls

the Frequency Synthesizer.

Figure 17. Ratio Feature Summary

Referenced Control

Register Location

Ratio......................................

“Ratio (Address 06h - 09h)” on page 27

LFRatioCfg ............................

“Low-Frequency Ratio Configuration (LFRatioCfg)” on page 29

RModSel[2:0] ........................

“R-Mod Selection (RModSel[2:0])” section on page 26

RefClkDiv[1:0] .......................

“Reference Clock Input Divider (RefClkDiv[1:0])” on page 28

Effective Ratio R

EFF

Ratio Format

Frequency Reference Clock

(CLK_IN)

SysClk

PLL Output

Frequency

Synthesizer

Digital PLL &

Fractional N Logic

N

Ratio

12.20

20.12

LFRatioCfg

RModSel[2:0]

Ratio

Modifier

R Correction

RefClkDiv[1:0]

Timing Reference Clock

(XTI/REF_CLK)

Divide

RefClkDiv[1:0]

User Defined Ratio R

UD