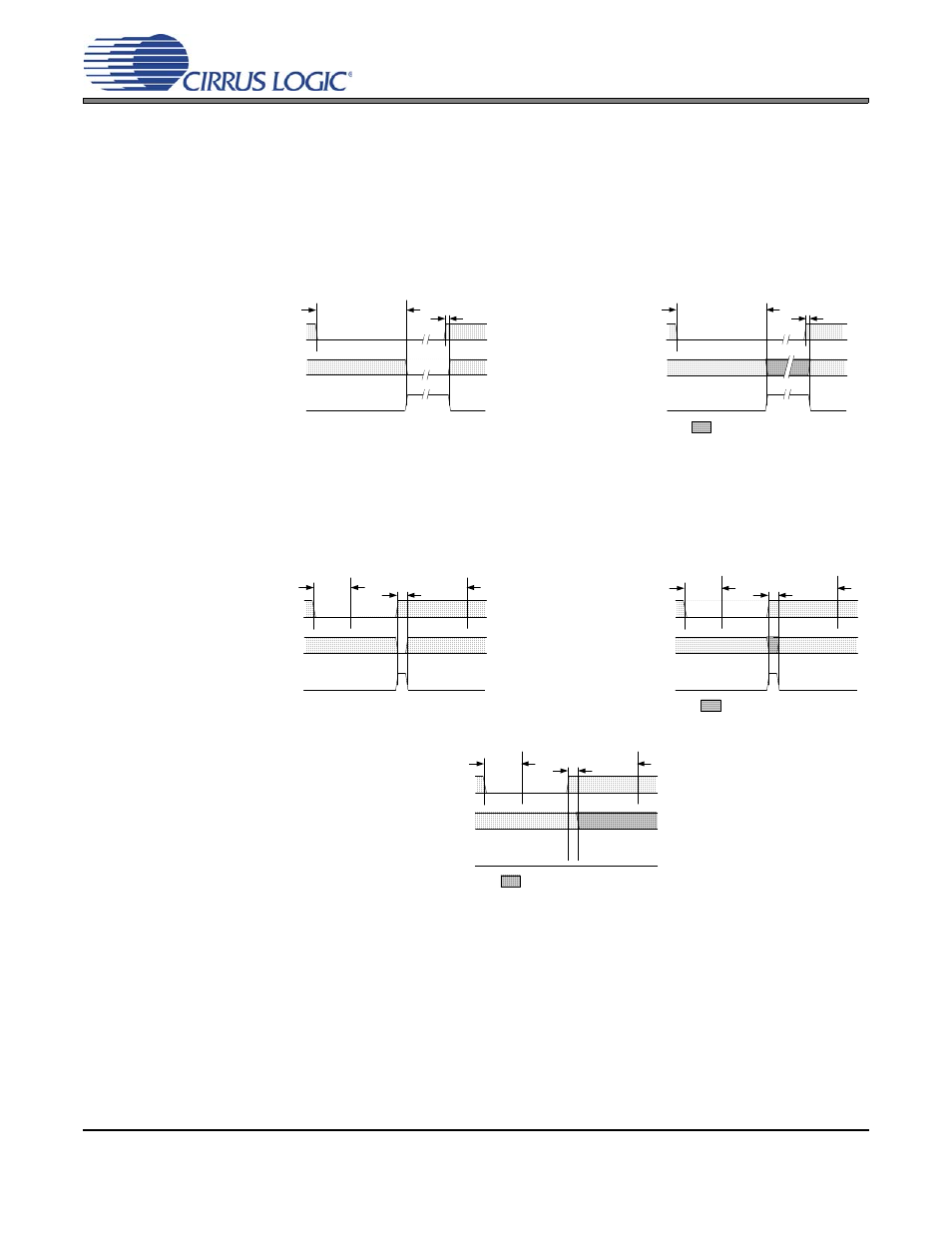

Figure 12. clk_in removed for > 2, Figure 13. clk_in removed for < 2, Cs2100-cp – Cirrus Logic CS2100-CP User Manual

Page 15

CS2100-CP

DS840F2

15

Regardless of the setting of the ClkSkipEn bit the PLL output will continue for 2

23

SysClk cycles (466 ms

to 1048 ms) after CLK_IN is removed (see

). This is true as long as CLK_IN does not glitch or

have an effective change in period as the clock source is removed, otherwise the PLL will interpret this as

a change in frequency causing clock skipping and the 2

23

SysClk cycle time-out to be bypassed and the

PLL to immediately unlock. If the prior conditions are met while CLK_IN is removed and 2

23

SysClk cycles

pass, the PLL will unlock and the PLL_OUT state will be determined by the ClkOutUnl bit; See

. If CLK_IN is re-applied after such time, the PLL will remain unlocked for the specified

time listed in the

“AC Electrical Characteristics” on page 7

after which lock will be acquired and the PLL

output will resume.

If it is expected that CLK_IN will be removed and then reapplied within 2

23

SysClk cycles but later than

t

CS

, the ClkSkipEn bit should be disabled. If it is not disabled, the device will behave as shown in

; note that the lower figure shows that the PLL output frequency may change and be incorrect

without an indication of an unlock condition.

Figure 12. CLK_IN removed for > 2

23

SysClk cycles

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0 or 1

ClkOutUnl=0

Lock Time

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0 or 1

ClkOutUnl=1

Lock Time

= invalid clocks

2

23

SysClk cycles

2

23

SysClk cycles

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0 or 1

ClkOutUnl=0

Lock Time

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn=0 or 1

ClkOutUnl=1

Lock Time

t

CS

t

CS

= invalid clocks

CLK_IN

PLL_OUT

UNLOCK

ClkSkipEn= 1

ClkOutUnl= 0 or 1

Lock Time

t

CS

= invalid clocks

2

23

SysClk cycles

2

23

SysClk cycles

2

23

SysClk cycles

Figure 13. CLK_IN removed for < 2

23

SysClk cycles but > t

CS