8 lpc bus components, 1 lpc bus overview, 2 super i/o chipset – IEI Integration PCISA-9652 v1.01 User Manual

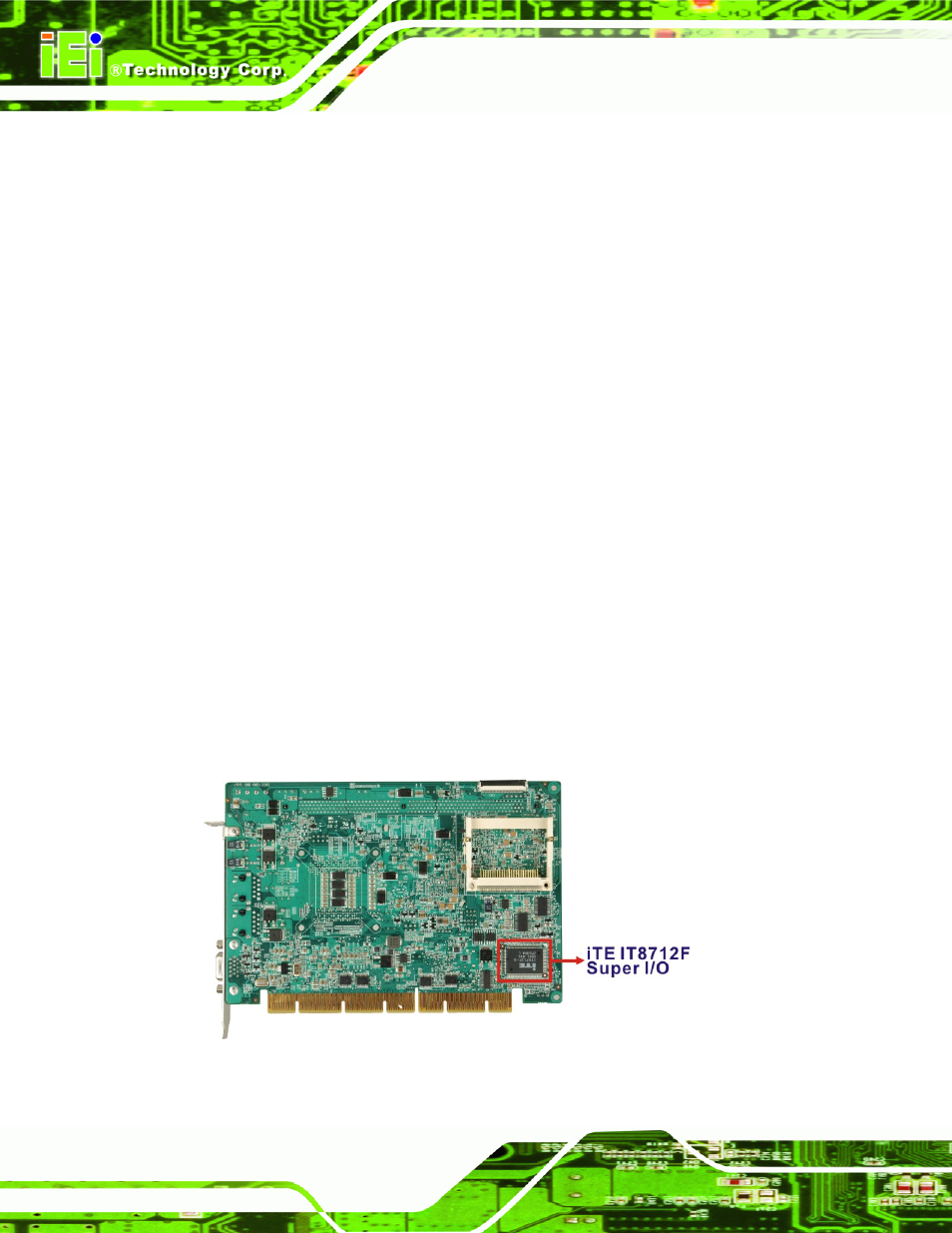

Page 46: 8 lpc b, Omponents, Figure 2-13: ite it8712f super i/o

PCISA-9652 Half-Size CPU Card

Page 26

Mechanism for reducing interrupts from Tx/Rx operations

Integrated PHY for 10/100/1000 Mbps (full- and half-duplex)

IEEE 802.3ab* auto-negotiation support

IEEE 802.3ab PHY compliance and compatibility

Tx/Rx IP,TCP,and UDP checksum offloading

Tx TCP segmentation

IEEE 802.1q* Virtual Local Area Network (VLAN) support with VLAN tag

insertion, stripping, and packet filtering for up to 4096 VLAN tags

Boot ROM Preboot eXecution Environment (PXE) Flash interface support

SDG 3.0,WfM 3.0 and PC2001 compliant

Wake on LAN support

2.8 LPC Bus Components

2.8.1 LPC Bus Overview

The LPC bus is connected to components listed below:

Super I/O chipset

2.8.2 Super I/O chipset

The iTE IT8712F Super I/O chipset is connected to the ICH8ME through the LPC bus. iTE

IT8712F Super I/O chipset is shown in Figure 2-13 below.

Figure 2-13: iTE IT8712F Super I/O