Qphy-sata software option – Teledyne LeCroy QPHY-SATA User Manual

Page 33

QPHY-SATA Software Option

915745 Rev

G

33

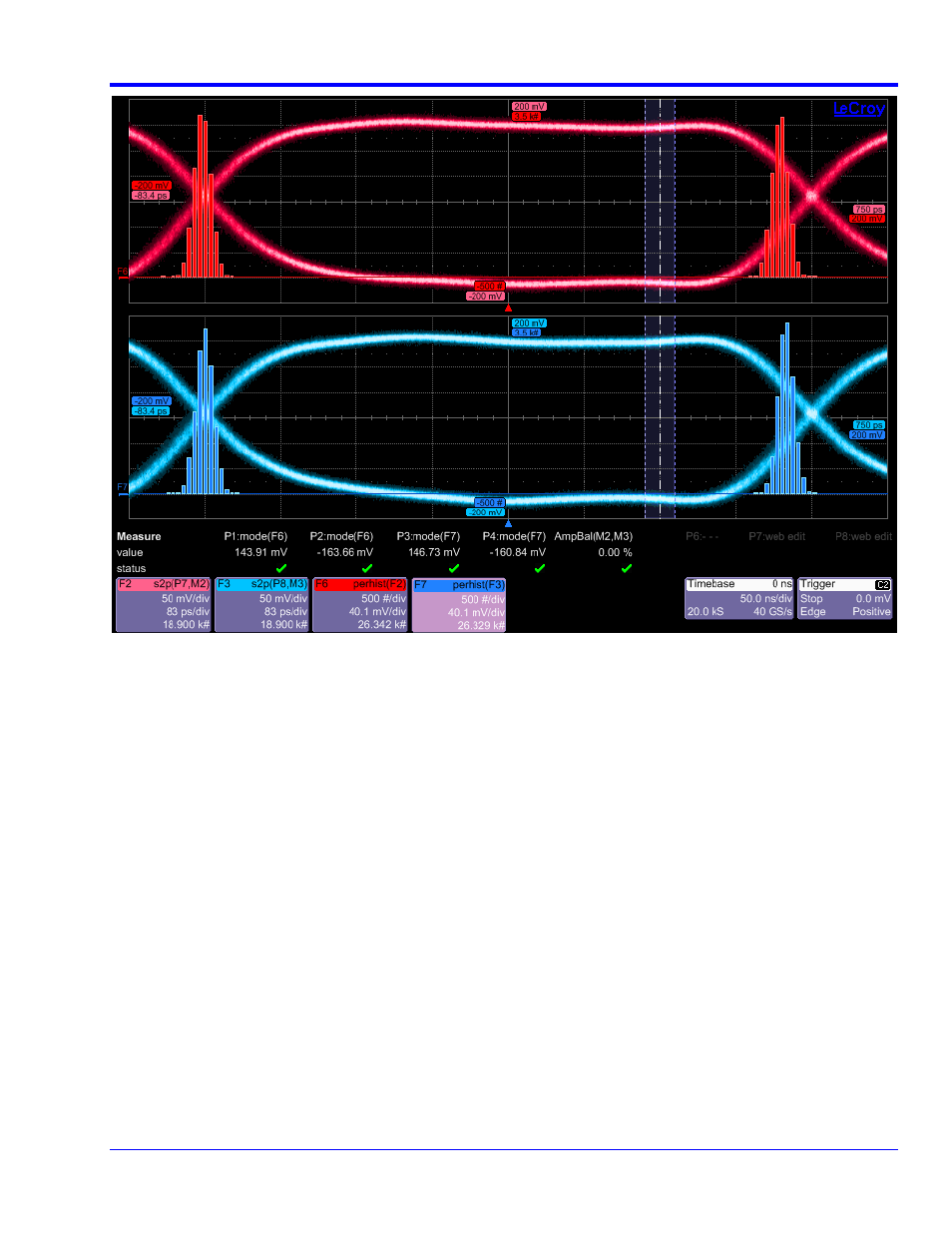

Figure 13. Amplitude Imbalance measurement on an MFTP pattern

The following tests measure the jitter, Total (Tj) and Deterministic (Dj), of the transmitter.

TSG-09

– Gen1 (1.5Gb/s) TJ at Connector, Clock to Data fBAUD/500

TSG-10

– Gen1 (1.5Gb/s) DJ at Connector, Clock to Data fBAUD/500

TSG-11

– Gen2 (3.0Gb/s) TJ at Connector, Clock to Data fBAUD/500

TSG-12

– Gen2 (3.0 GB/s) DJ at Connector, Clock to Data fBAUD/500

In the past, these tests had different implementations for products running at 1.5Gb/s and 3.0Gb/s. Currently, the

implementation is the same, but the test names have been left as is. The jitter is measured using a phase-locked

loop (PLL) to recover the clock. To tune the clock recovery to the precise response dictated by the Jitter Transfer

Function in the SATA specification, follow the calibration procedure for jitter measurement devices. Jitter is

measured on HFTP, MFTP and SSOP. The SSOP pattern is optional.

- WaveAce EasyScope Operators Manual (28 pages)

- PeRT3 Software Interface (15 pages)

- FireInspector Automation Application Programming Interface (92 pages)

- PETracer ProtoSync Software User Manual (154 pages)

- QPHY-PCIe3-Tx-Rx (32 pages)

- Signal Integrity Studio (14 pages)

- Serial Data Debug Solutions (204 pages)

- Line Code and Symbolic Decoders (20 pages)

- AORM - Advanced Optical Recording Measurements (125 pages)

- CANbus TD - Quick Reference Guide (8 pages)

- CANbus TD and CANbus TDM - Operators Manual (69 pages)

- FlexRay Trigger, Decode and Physical Layer Test (32 pages)

- MIPI D-PHY (15 pages)

- DFP2 - Digital Filter Package 2 (22 pages)

- ET-PMT - Electrical Telecom Pulse Mask Testing (11 pages)

- ENETbusD Decoder (16 pages)

- Eye Doctor II (45 pages)

- JitKit (16 pages)

- JTA2 (31 pages)

- Power Analyzer Package (34 pages)

- QPHY-10GBase-KR (28 pages)

- QPHY-10GBase-T (36 pages)

- QPHY-BroadR-Reach (33 pages)

- QPHY-DDR2 (47 pages)

- QPHY-DDR3 (44 pages)

- QPHY-DDR4 (73 pages)

- QPHY-DisplayPort (19 pages)

- QPHY-ENET (78 pages)

- QPHY-HDMI (37 pages)

- QPHY-LPDDR2 (49 pages)

- QPHY-MIPI-DPHY (32 pages)

- QPHY-MOST150 (24 pages)

- QPHY-MOST50 (21 pages)

- QPHY-PCIe (30 pages)

- QPHY-PCIE3 (28 pages)

- QPHY-SAS2 (45 pages)

- QPHY-SAS3 (50 pages)

- QPHY-USB (66 pages)

- QPHY-USB3-Tx-Rx (47 pages)

- QPHY-UWB (30 pages)

- SDA II (38 pages)

- SDA III-CompleteLinQ (59 pages)

- Spectrum Analyzer (14 pages)

- USB2 Decoder (24 pages)