Qphy-mipi-dphy software option – Teledyne LeCroy QPHY-MIPI-DPHY User Manual

Page 29

QPHY-MIPI-DPHY Software Option

918841 Rev

A

29

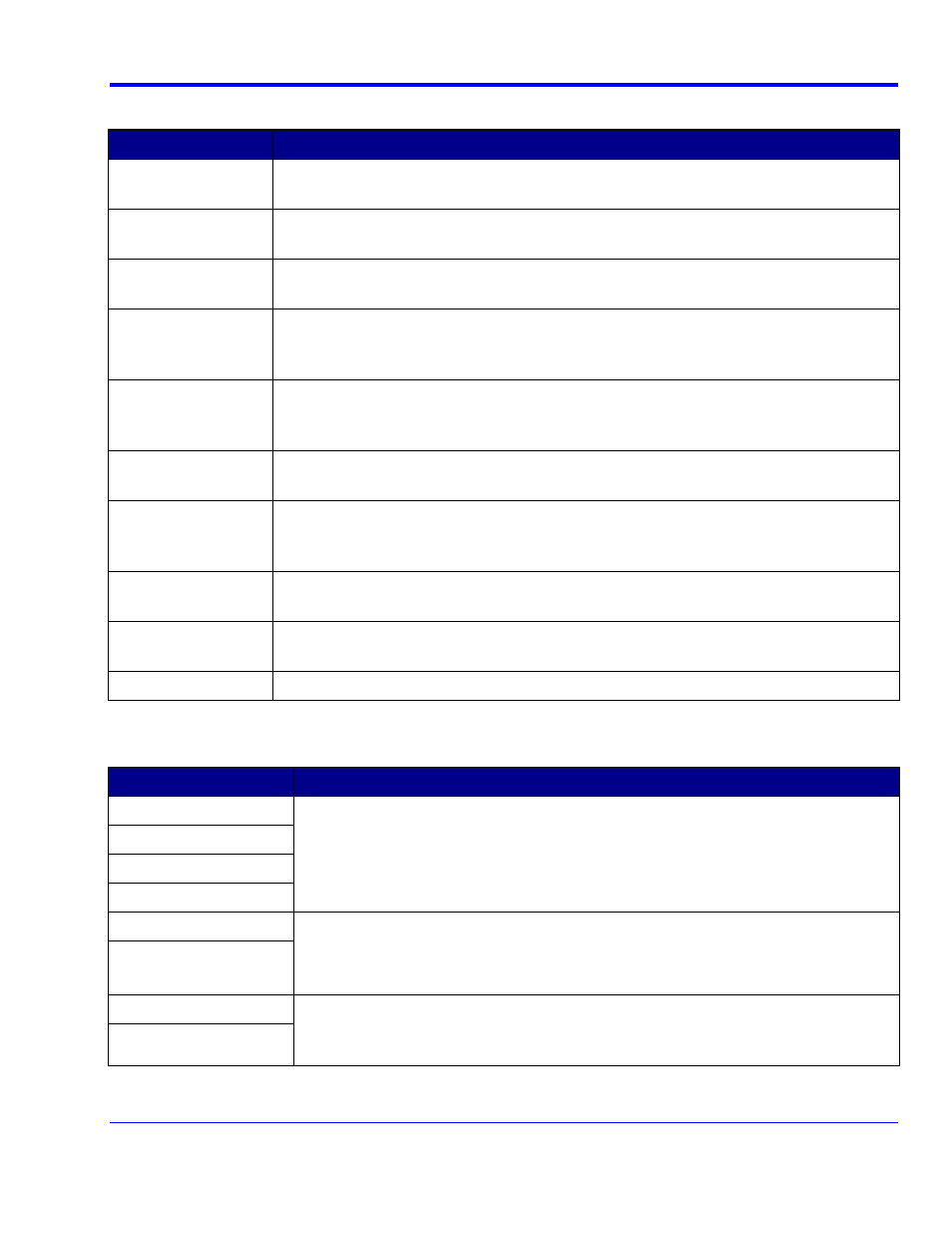

BRIEF HS CLOCK TIMING TEST DESCRIPTIONS

Name

Purpose

TLP-01

To verify that the duration (TLPX) of the final Clock Lane LP-01 state immediately before

HS transmission is greater than the minimum conformant value.

TCLK-PREPARE

To verify that the time that the DUT Clock Lane transmitter drives LP-00 (TCLK-PREPARE)

prior to driving TCLK-ZERO when entering HS mode, is within the conformance limits.

TCLK-ZERO

To verify the time that the DUT Clock Lane transmitter drives the extended HS-0

differential state prior to starting clock transmission

TCLK-PREPARE+ZERO

To verify that the combined time of TCLK-PREPARE plus the time that the DUT Clock Lane

transmitter drives the extended HS-0 differential state prior to starting clock

transmission (TCLK-ZERO) is greater than the minimum required duration.

TCLK-TRAIL

To verify that the duration that the DUT Clock Lane HS transmitter drives the final HS-0

differential state following the last payload clock bit of a HS transmission burst (TCLK-

TRAIL) is greater than the minimum required value.

TREOT

To verify that the 30%-85% Post-EoT Rise Time (TREOT) of the DUT LP Clock Lane

transmitter is within the conformance limits.

TEOT

To verify that the interval measured from the start of the DUT Clock Lane HS

transmitter’s TCLK-TRAIL to the start of the first Clock Lane LP-11 state (TEOT) is less

than the maximum allowed limit.

THS-EXIT

To verify that the duration that the Clock Lane transmitter remains in the LP-11 (Stop)

state after exiting HS mode (THS-EXIT), is greater than the minimum required value.

UIinst

To verify that the Instantaneous Unit Interval values (UIINST) of the DUT HS Clock are

within the conformance limits.

HS-Bitrate

To verify the Bitrate of the DUT HS Clock is within conformance limits.

BRIEF HS COMMON MODE TEST DESCRIPTIONS

Name

Purpose

VCMTX-DATA-1

To verify that the Static Common-Mode Voltages (VCMTX(1), and VCMTX(0)) of the

DUT Data & Clock Lanes HS transmitter are within the conformance limits.

VCMTX-DATA-0

VCMTX-CLK-1

VCMTX-CLK-0

dVCMTXLF-DATA

To verify that the AC Common-Mode Signal Level Variations between 50 and 450MHz

(ΔVCMTX(LF)) of the DUT Data & Clock Lanes HS transmitter are less than the

maximum allowable limit.

dVCMTXLF-CLK

dVCMTXHF-DATA

To verify that the AC Common-Mode Signal Level Variations above 450MHz

(ΔVCMTX(HF)) of the DUT Data & Clock Lanes HS transmitter are less than the

maximum allowable limit.

dVCMTXHF-CLK