Hs (high speed) tests – Teledyne LeCroy QPHY-MIPI-DPHY User Manual

Page 28

28

918841 Rev

A

HS (High Speed) Tests

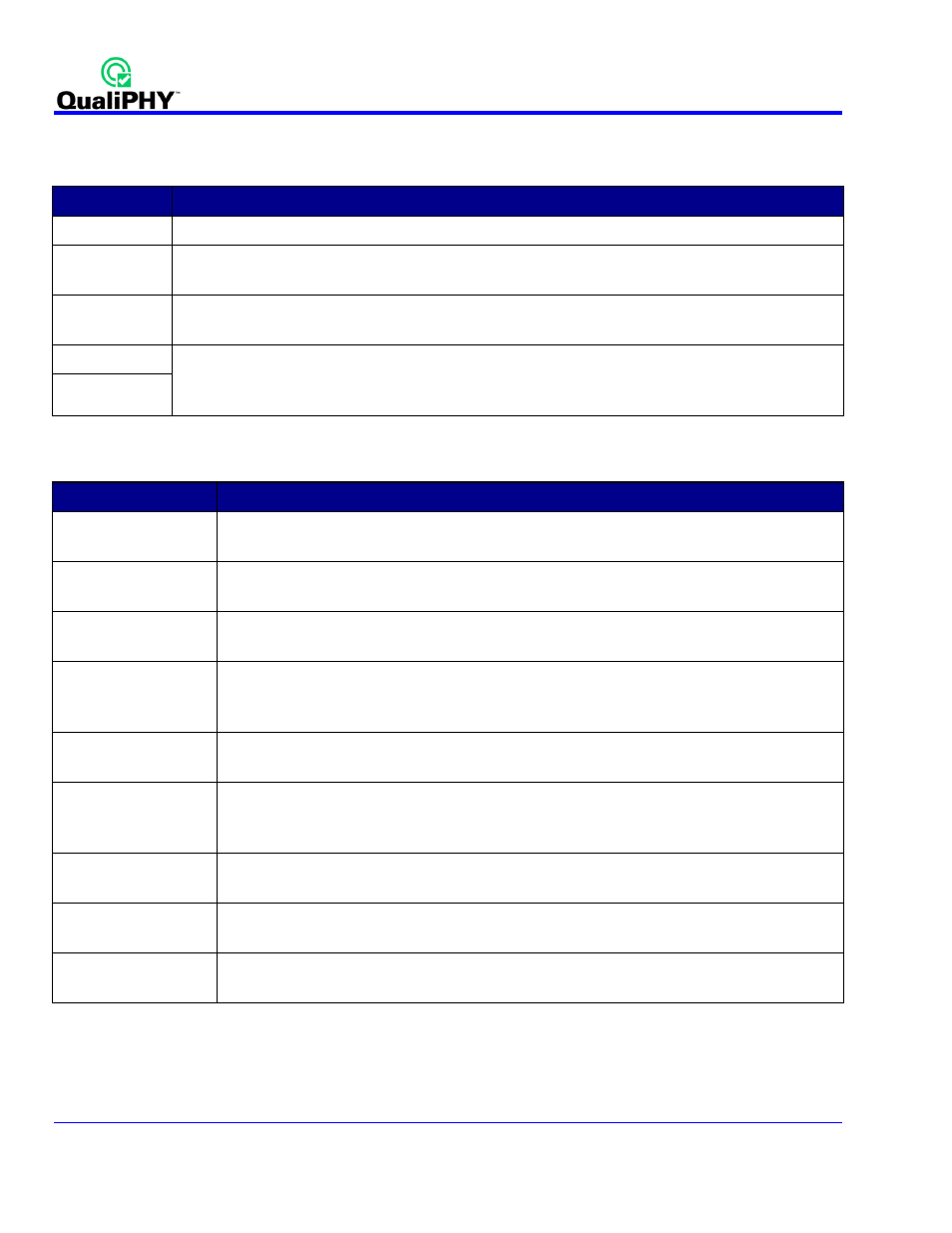

BRIEF HS CLOCK TO DATA TIMING TEST DESCRIPTIONS

Name

Purpose

FirstBit

To verify that the DUT HS Clock is properly aligned to the payload data signaling.

TCLK-PRE

To verify that the time that the HS clock is driven prior to an associated Data Lane beginning

the transition from LP to HS mode (TCLK-PRE), is greater than the minimum required value.

TCLK-POST

To verify that the DUT Clock Lane HS transmitter continues to transmit clock signaling for the

minimum required duration (TCLK-POST) after the last Data Lane switches to LP mode.

TSETUP

QualiPHY is using the oscilloscope’s TSETUP measure to compute TSKEW (= TSETUP – UI/2).

TSKEW (min, max and average results) are written in report. TSETUP & THOLD are

intermediate results not written in report.

THOLD

BRIEF HS DATA TIMING TEST DESCRIPTIONS

Name

Purpose

TLP-01

To verify that the duration (TLPX) of the final Data Lane LP-01 state immediately before

HS transmission is greater than the minimum conformant value.

THS-PREPARE

To verify that the duration of the final LP-00 state immediately before HS transmission

(THS-PREPARE) is within the conformance limits.

THS-ZERO

To verify the time the DUT Data Lane transmitter drives the HS-0 differential state prior

to transmitting the HS Sync sequence

THS-PREPARE+ZERO

To verify that the combined time of THS-PREPARE plus the time the DUT Data Lane

transmitter drives the HS-0 differential state prior to transmitting the HS Sync sequence

(THS-ZERO) is greater than the minimum required duration.

THS-SYNC

To verify the time to transmit the HS Sync sequence before the first bit of data is

transmitted

THS-TRAIL

To verify that the duration the DUT Data Lane TX drives the inverted final differential

state following the last payload data bit of a HS-TX burst (THS-TRAIL), is greater than the

minimum required value.

TEOT

To verify that the combined duration of the THS-TRAIL plus TREOT intervals (a.k.a. TEOT)

of the DUT Data Lane transmitter is less than the maximum allowed value.

TREOT

To verify that the 30%-85% Post-EoT Rise Time (TREOT) of the DUT LP Data Lane

transmitter is within the conformance limits.

THS-EXIT

To verify that the duration that the Data Lane transmitter remains in the LP-11 (Stop)

state after exiting HS mode (THS-EXIT), is greater than the minimum required value.