Impulse PIO-48.PC104 (3701) User Manual

Page 16

© Sealevel Systems, Inc.

- 14 -

PIO-48.PC104 User Manual

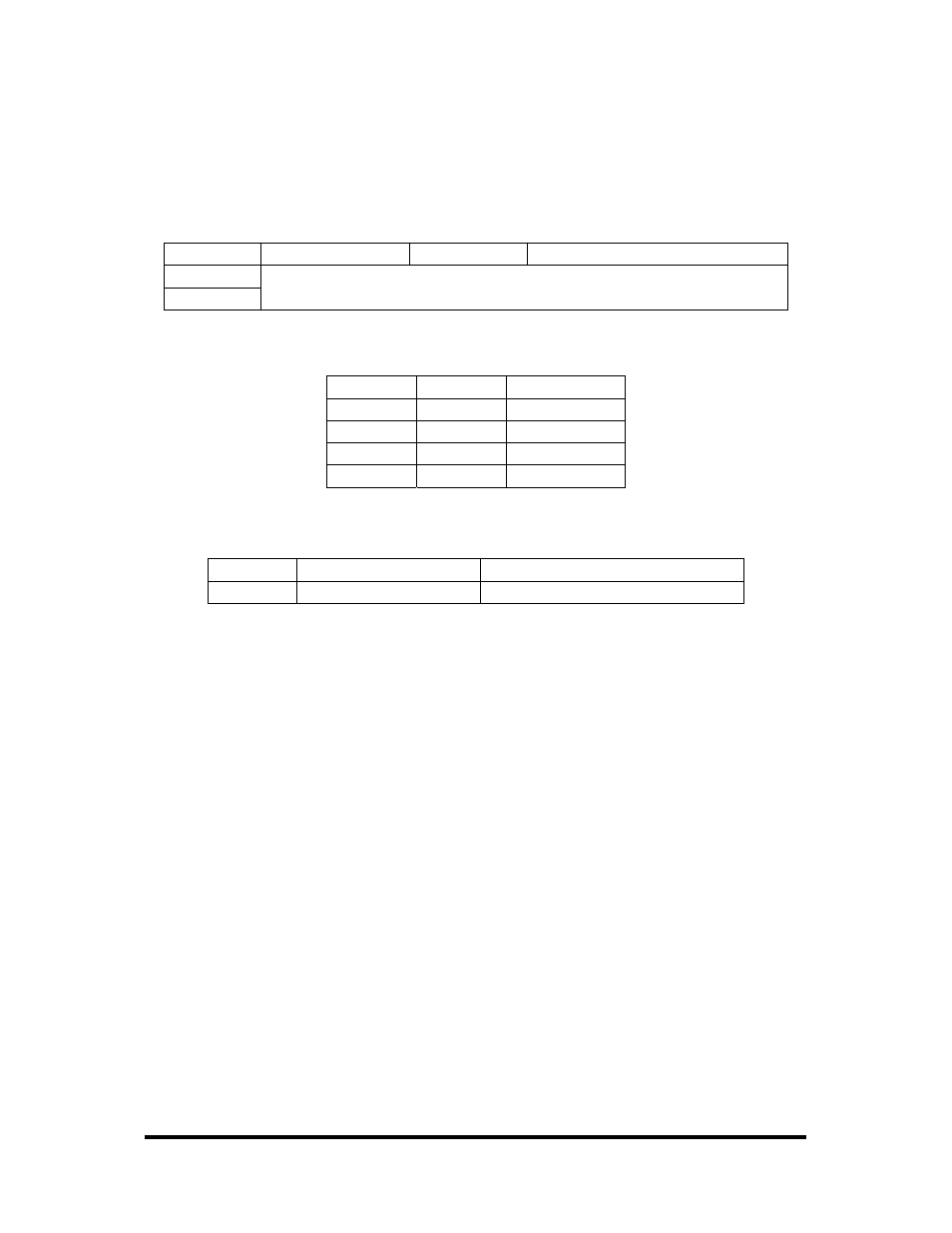

Interrupt Control

When enabled interrupts are generated on port bit A0 of each port (pin 47 on each

50 pin header), the port A0 must be set as an input.

X = port number

IRQENX

interrupt enable

1 = enabled

0 = disabled ( 0 on power up )

IRQCX0

IRQCX1

Interrupt mode select see table

Interrupt mode select see table

Interrupt mode select table

IRQCn1 IRQCn0 INT

Type

0 0

Low

level

0 1

High

level

1 0

Falling

edge

1 1

Rising

edge

Interrupt Read

Reading the INTSTAT port (Base+5) clears any interrupt pending.

IRQST1

(D0) Interrupt status

1 = interrupt pending, 0 = none

IRQST2

(D4) Interrupt status

1 = interrupt pending, 0 = none

See also other documents in the category Impulse Hardware:

- PCW-5181 (120 pages)

- PCM-4373 (2 pages)

- EPIC-5536 (2 pages)

- EPIC-CV07 (2 pages)

- EPIC-QM57 (2 pages)

- EPIC-QM77 (2 pages)

- VSX-6118-V2 (1 page)

- VSX-6116-V2 (1 page)

- VSX-6115-V2 (1 page)

- VSX-6114-V2 (1 page)

- VDX-6318RD (1 page)

- VDX-6316RD (1 page)

- VDX-6315RD (1 page)

- VDX-6314RD (1 page)

- PCM-5895 Rev. A (2 pages)

- PCM-8120 (2 pages)

- PCM-9562 (3 pages)

- VSX-6127-V2 (1 page)

- PCM-9375 (3 pages)

- GENE-5315W1 Rev. B (2 pages)

- GENE-5315 Rev. A (2 pages)

- VDX-6327RD (1 page)

- VDX-6328RD (1 page)

- VDX-6329RD (1 page)

- VDX-6326RD (1 page)

- PCM-9343 (3 pages)

- GENE-9655 (2 pages)

- PCM-9362 (2 pages)

- GENE-LN05W2 Rev. B (2 pages)

- PCM-9363 (3 pages)

- GENE-TC05W2 (2 pages)

- GENE-CV05W2 (2 pages)

- SBC-210 (1 page)

- GENE-QM57 (2 pages)

- GENE-QM67 (2 pages)

- GENE-QM77 Rev B (2 pages)

- GENE-QM77 Rev A (2 pages)

- GENE-QM87 (1 page)

- EL630-NR (2 pages)

- EL620-C (2 pages)

- SB601-C (2 pages)

- SB600-C (2 pages)

- SB630-CRM (2 pages)

- CL630-CRM (2 pages)

- DL631-C226 (2 pages)