External hardware level trigger mode – Ocean Optics External Triggering Options Instructions for Spectrometers with Firmware Version 3.0 and Above User Manual

Page 8

External Triggering Options Instructions for FW 3.0 and Above

8

200-00000-001-01-201401

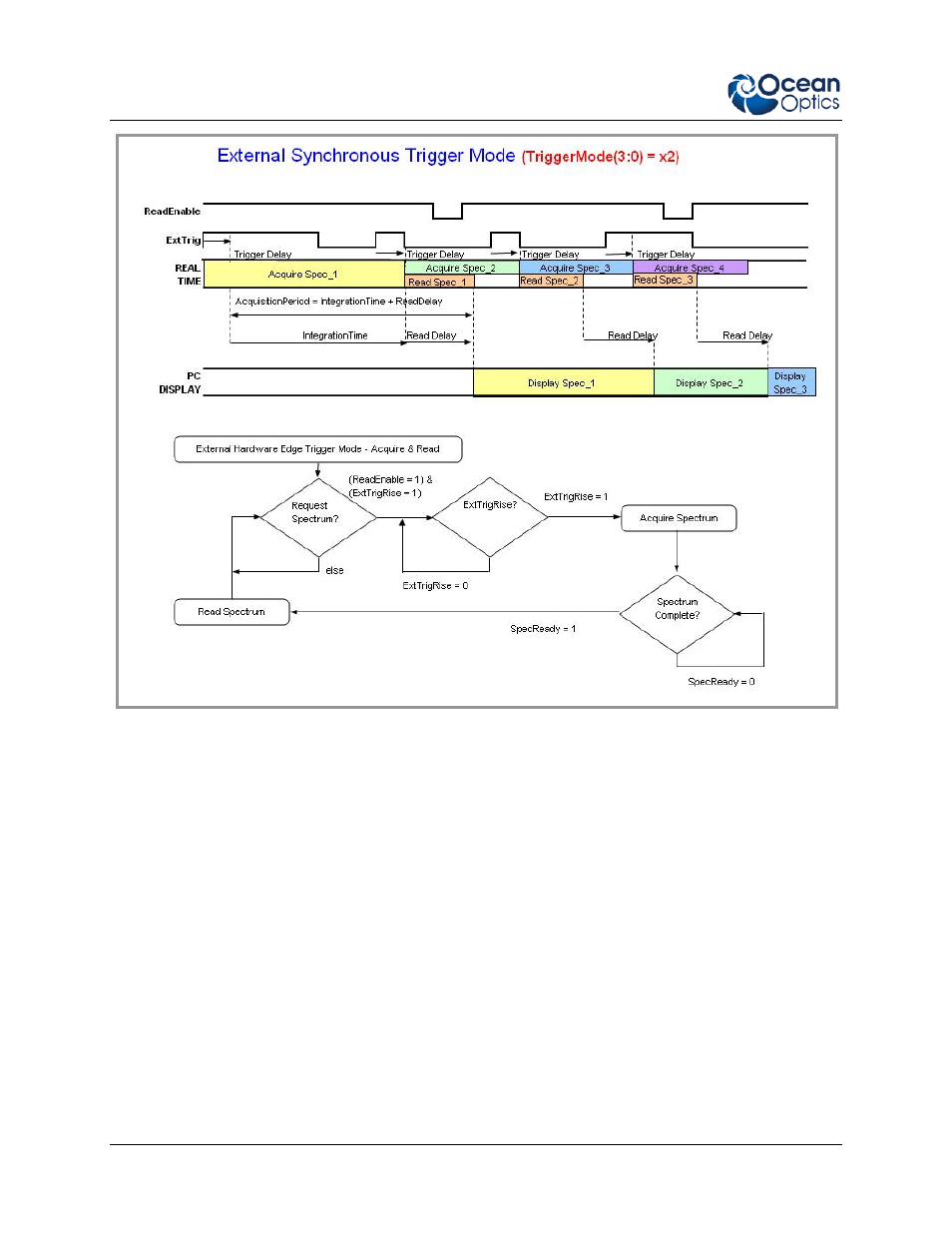

External Synchronous Trigger Mode Timing Sequence

External Hardware Level Trigger Mode

In the External Hardware Level Trigger mode, a rising edge detected by the FPGA from the External

Trigger input starts the Integration Cycle specified through the software interface. After the Integration

Cycle completes, the spectrum is retrieved and written to the FIFO in the FPGA. As long as the trigger

level remains active in a logic one state, continuous acquisitions will occur with the following exception.

Each subsequent acquisition must wait until a minimum CCD Reset Cycle completes. This Reset Cycle

insures that the CCD performance uniform on a scan-to-scan basis. The time duration for this reset cycle

is relative to the Integration Cycle time and will change if the integration period is changed. So the

timing sequence is Trigger, Trigger Delay, Integration Cycle, Read/Write Cycle, Reset Cycle, Idle

Cycle(s), and Integration Cycle (if trigger is still high). The Idle Cycle will on last 2 µs if the trigger

remains high and the FIFO is empty and a spectrum request is active, otherwise the Idle Cycle will

continue until all 3 conditions are satisfied.