Rainbow Electronics MAX3799 User Manual

Page 23

MAX3799

1Gbps to 14Gbps, SFP+ Multirate Limiting

Amplifier and VCSEL Driver

______________________________________________________________________________________

23

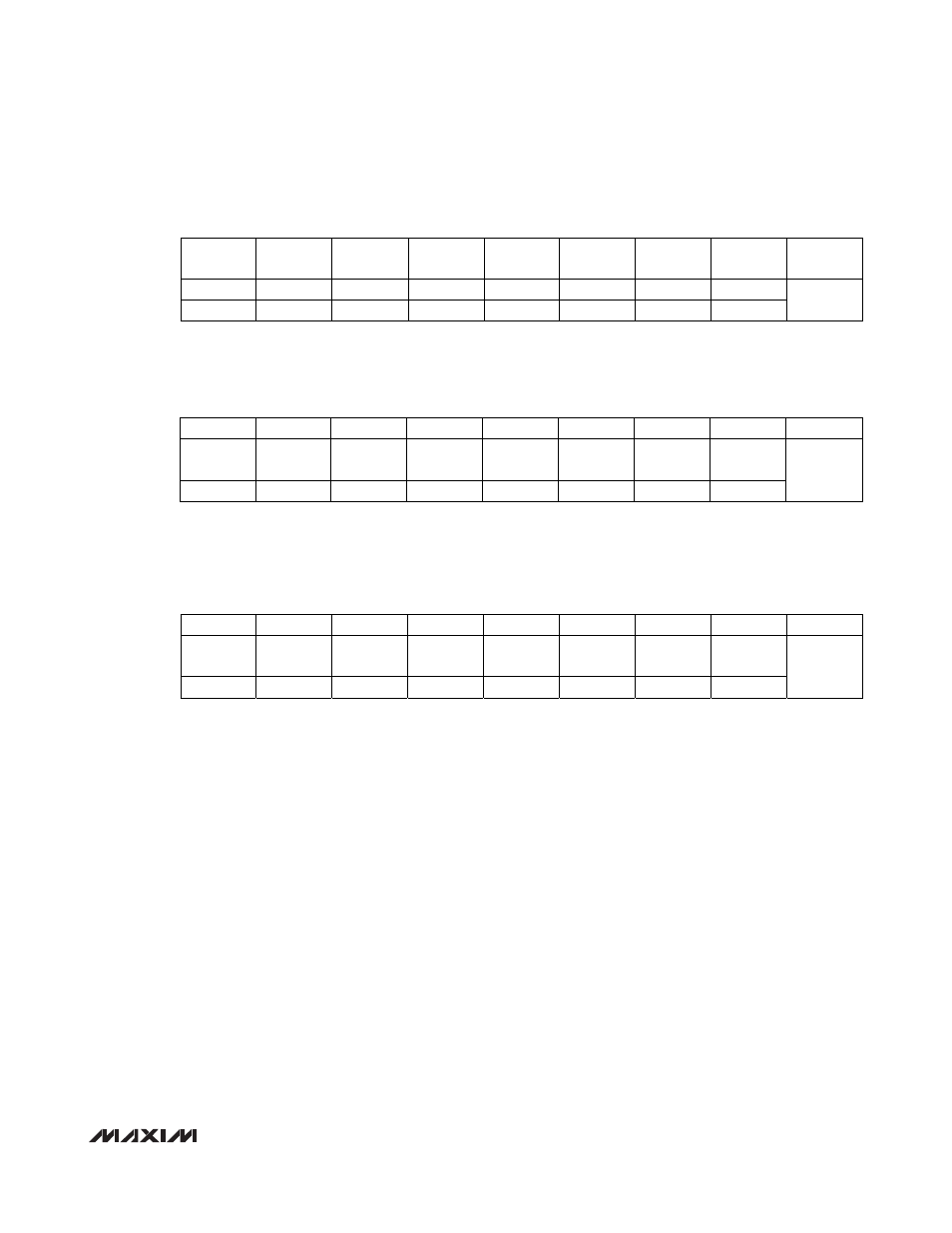

Receiver Status Register (RXSTAT)

Bit 0: LOS. Copy of the LOS output circuitry. This is a sticky bit, which means that it is cleared on a read. The first

0-to-1 transition gets latched until the bit is read by the master or POR occurs.

Output CML Level Setting Register (SET_CML)

Bits 7 to 0: SET_CML[7:0]. The SET_CML register is an 8-bit register that can be set up to 255, corresponding to an

output up to 1000mV

P-P

. See the

Typical Operating Characteristics

section for a typical CML output voltage vs. DAC

code graph.

LOS Threshold Level Setting Register (SET_LOS)

Bits 5 to 0: SET_LOS[5:0]. The SET_LOS register is a 6-bit register used to program the LOS threshold. See the

Typical Operating Characteristics

section for a typical LOS threshold voltage vs. DAC code graph.

Bit #

7 6 5 4 3 2 1

0

(STICKY)

ADDRESS

Name

X X X X X X X

LOS

Default

Value

X X X X X X X X

H0x02

Bit #

7 6 5 4 3 2 1 0

ADDRESS

Name

SET_CML[7]

(MSB)

SET_CML[6] SET_CML[5] SET_CML[4] SET_CML[3] SET_CML[2] SET_CML[1]

SET_CML[0]

(LSB)

Default

Value

0 1 0 1 0 0 1 1

H0x03

Bit #

7 6 5 4 3 2 1 0

ADDRESS

Name X

X

SET_LOS[5]

(MSB)

SET_LOS[4] SET_LOS[3] SET_LOS[2] SET_LOS[1]

SET_LOS[0]

(LSB)

Default

Value

X X 0 0 1 1 0 0

H0x04