Max109, Ac electrical characteristics (continued) – Rainbow Electronics MAX109 User Manual

Page 6

MAX109

8-Bit, 2.2Gsps ADC with Track/Hold Amplifier

and 1:4 Demultiplexed LVDS Outputs

6

_______________________________________________________________________________________

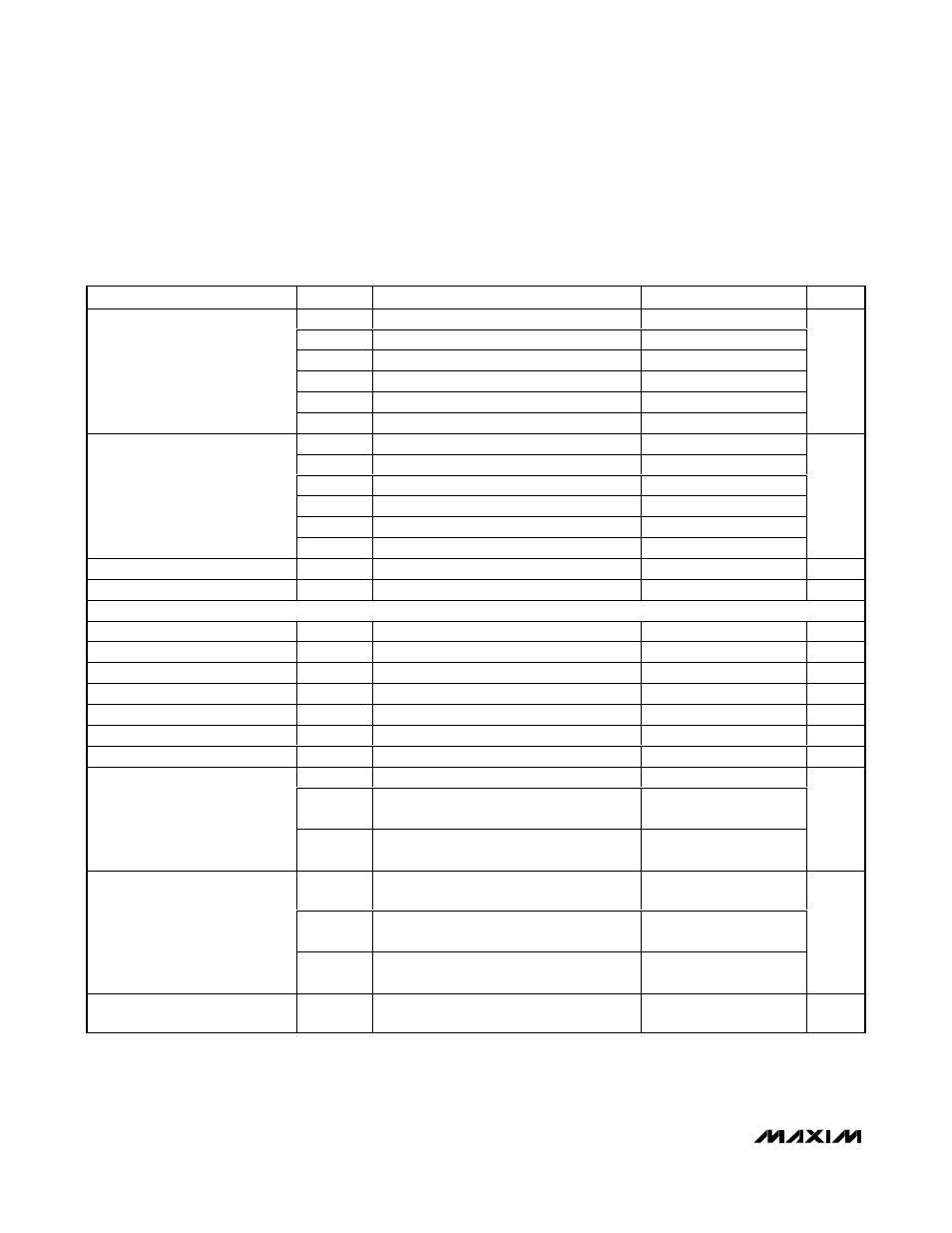

AC ELECTRICAL CHARACTERISTICS (continued)

(V

CC

A = V

CC

I = V

CC

D = 5V, V

CC

O = 3.3V, V

EE

= -5V, GNDA = GNDI = GNDD = GNDO = GNDR = 0V, f

CLK

= 2.2Gsps, analog input

amplitude at -1dBFS differential, clock input amplitude 400mV

P-P

differential, digital output pins differential R

L

= 100Ω. Typical values

are at T

A

= +25°C, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SFDR

300

f

IN

= 300MHz, f

CLK

= 2.2Gsps

61.7

SFDR

1000

f

IN

= 1000MHz, f

CLK

= 2.2Gsps (Note 8)

44.4

51.1

SFDR

1600

f

IN

= 1600MHz, f

CLK

= 2.2Gsps (Note 8)

43.7

50.3

SFDR

2500

f

IN

= 2500MHz, f

CLK

= 2.2Gsps

45.0

SFDR

500

f

IN

= 500MHz, f

CLK

= 2.5Gsps

53.7

Spurious Free Dynamic Range

SFDR

1600

f

IN

= 1600MHz, f

CLK

= 2.5Gsps

44.6

dBc

SINAD

300

f

IN

= 300MHz, f

CLK

= 2.2Gsps

44.1

SINAD

1000

f

IN

= 1000MHz, f

CLK

= 2.2Gsps (Note 8)

40.4

43.1

SINAD

1600

f

IN

= 1600MHz, f

CLK

= 2.2Gsps (Note 8)

37.9

42.1

SINAD

2500

f

IN

= 2500MHz, f

CLK

= 2.2Gsps

40.1

SINAD

500

f

IN

= 500MHz, f

CLK

= 2.5Gsps

43.1

Signal-to-Noise-Plus-Distortion

Ratio

SINAD

1600

f

IN

= 1600MHz, f

CLK

= 2.5Gsps

40.5

dB

Third-Order Intermodulation

IM3

f

IN1

= 1590MHz, f

IN2

= 1610MHz at -7dBFS

-60

dBc

Metastability Probability

10

-14

TIMING CHARACTERISTICS

Maximum Sample Rate

f

CLK(MAX)

2.2

Gsps

Clock Pulse-Width Low

t

PWL

t

CLK

= t

PWL

+ t

PWH

(Note 8)

180

ps

Clock Pulse-Width High

t

PWH

t

CLK

= t

PWL

+ t

PWH

(Note 8)

180

ps

Aperture Delay

t

AD

200

ps

Aperture Jitter

t

AJ

0.2

ps

Reset Input Data Setup Time

t

SU

(Note 8)

300

ps

Reset Input Data Hold Time

t

HD

(Note 8)

250

ps

t

PD1

DCO = f

CLK

/ 4, CLK fall to DCO rise time

1.6

t

PD1DDR

DCO = f

CLK

/ 8, DDR mode, CLK fall to

DCO rise time

1.6

CLK-to-DCO Propagation Delay

t

PD1QDR

DCO = f

CLK

/ 16, QDR mode, CLK fall to

DCO rise time

1.6

ns

t

PD2

DCO = f

CLK

/ 4, DCO rise to data transition

(Note 8)

-520

+520

t

PD2DDR

DCO = f

CLK

/ 8, DDR mode, DCO rise to

data transition (Note 8)

-520 +

2t

CLK

2t

CLK

520 +

2t

CLK

DCO-to-Data Propagation Delay

t

PD2QDR

DCO = f

CLK

/ 16, QDR mode, DCO rise to

data transition (Note 8)

-520 +

2t

CLK

2t

CLK

520 +

2t

CLK

ps

DCO Duty Cycle

Clock mode independent

45 to

55

%