Rainbow Electronics MAX1326 User Manual

Page 5

MAX1316–MAX1318/MAX1320–MAX1322/MAX1324–MAX1326

8-/4-/2-Channel, 14-Bit, Simultaneous-Sampling ADCs

with ±10V, ±5V, and 0 to +5V Analog Input Ranges

_______________________________________________________________________________________

5

Note 1:

For the MAX1316/MAX1317/MAX1318, V

IN

= 0 to +5V. For the MAX1320/MAX1321/MAX1322, V

IN

= -5V to +5V. For the

MAX1324/MAX1325/MAX1326, V

IN

= -10V to +10V.

Note 2:

All channel performance is guaranteed by correlation to a single channel test.

Note 3:

Offset nulled.

Note 4:

The analog input resistance is terminated to an internal bias point. Calculate the analog input current using:

for V

CH

within the input voltage range.

Note 5:

Throughput rate is given per channel. Throughput rate is a function of clock frequency (f

CLK

= 10MHz). See the Data

Throughput section for more information.

Note 6:

All analog inputs are driven with an FS 100kHz sine wave.

I

V

V

R

CH

CH

BIAS

CH

_

_

_

=

−

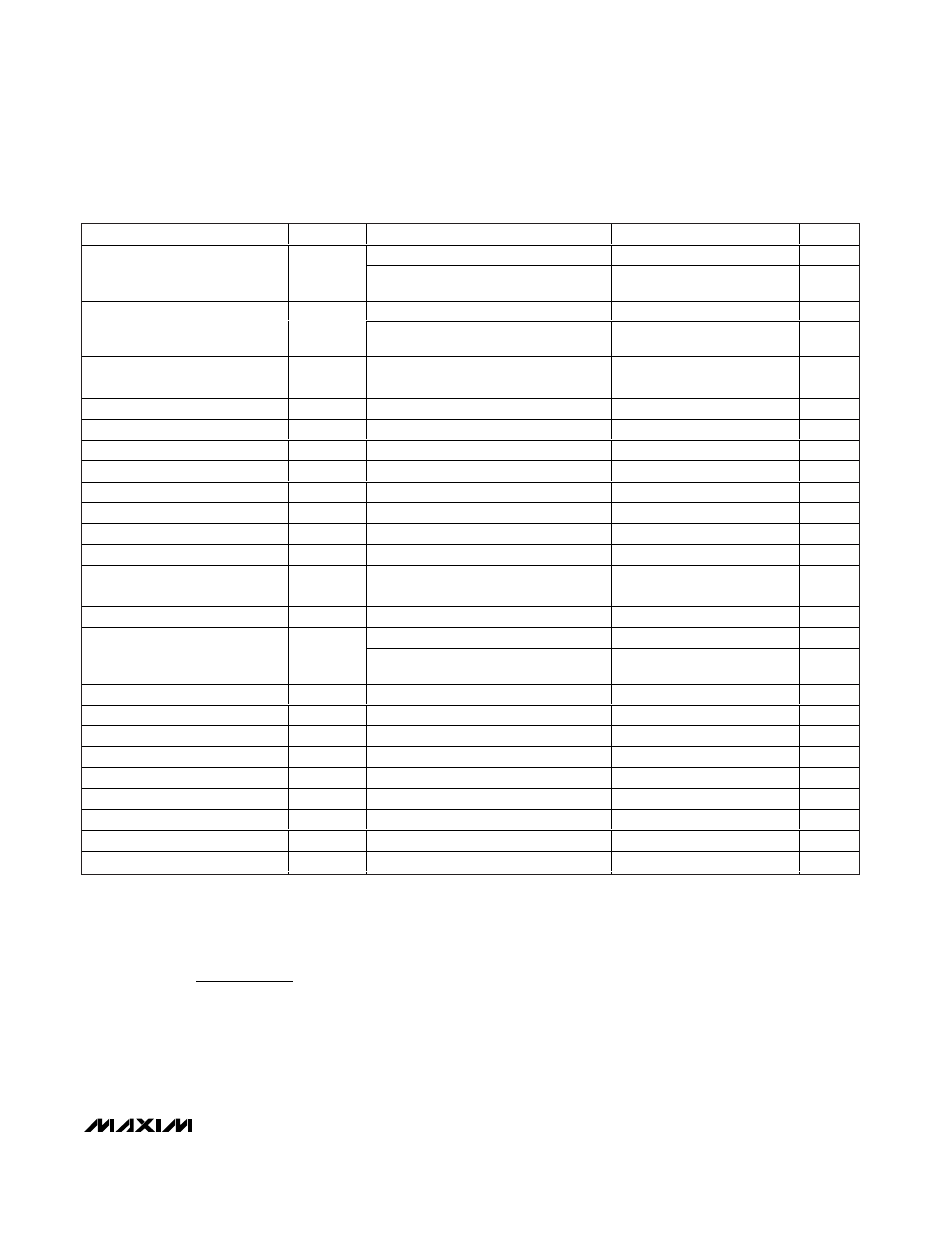

TIMING CHARACTERISTICS (Figures 3, 4, 5, 6 and 7) (Tables 1, 3)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Internal clock

1.6

1.8

µs

Time-to-First-Conversion Result

t

CONV

External clock, Figure 6

16

Clock

cycles

Internal clock

0.3

0.36

µs

Time-to-Next-Conversion Result

t

NEXT

External clock, Figure 6

3

Clock

cycles

CONVST Pulse-Width Low

(Acquisition Time)

t

ACQ

(Note 9)

0.16

100

µs

CS Pulse Width

t

2

30

ns

RD Pulse-Width Low

t

3

30

ns

RD Pulse-Width High

t

4

30

ns

WR Pulse-Width Low

t

5

30

ns

CS to WR

t

6

(Note 10)

ns

WR to CS

t

7

(Note 10)

ns

CS to RD

t

8

(Note 10)

ns

RD to CS

t

9

(Note 10)

ns

Data-Access Time

(RD Low to Valid Data)

t

10

30

ns

Bus-Relinquish Time (RD High)

t

11

30

ns

Internal clock

80

ns

EOC Pulse Width

t

12

External clock, Figure 6

1

Clock

cycles

Input-Data Setup Time

t

14

10

ns

Input-Data Hold Time

t

15

10

ns

External-Clock Period

t

16

0.08

10.00

µs

External-Clock High Period

t

17

Logic sensitive to rising edges

20

ns

External-Clock Low Period

t

18

Logic sensitive to rising edges

20

ns

External-Clock Frequency

(Note 11)

0.1

12.5

MHz

Internal-Clock Frequency

10

MHz

CONVST High to CLK Edge

t

19

20

(Note 12)

ns

EOC Low to RD

t

20

0

ns