Output coding and transfer function – Rainbow Electronics MAX1168 User Manual

Page 23

MAX1167/MAX1168

Multichannel, 16-Bit, 200ksps Analog-to-Digital

Converters

______________________________________________________________________________________

23

The input data latches on the falling edge of SCLK. The

command/configuration/control register starts reading

data in on the falling edge of the first SCLK cycle immedi-

ately following the falling edge of the frame sync pulse

and ends on the falling edge of the 16th SCLK cycle. The

MAX1168 selects the proper channel for conversion on

the falling edge of the 3rd clock cycle and begins acqui-

sition. Acquisition continues until the rising edge of the

15th clock cycle. The MAX1168 samples the input on the

rising edge of the 15th clock cycle. On the rising edge of

the 16th clock cycle, the MAX1168 outputs a frame sync

pulse at DSPX. The frame sync pulse alerts the DSP that

the conversion results are about to be output at DOUT

(MSB first) starting on the rising edge of the 17th clock

pulse. To read the entire conversion result, 16 SCLK

cycles are needed. Extra clock pulses, occurring after the

conversion result has been clocked out and prior to the

next rising edge of DSPR, cause zeros to be clocked out

of DOUT. The MAX1168 external clock, DSP 16-bit-wide

data-transfer mode requires 32 clock cycles to complete.

Begin a new conversion by sending a new frame sync

pulse to DSPR followed by new configuration data.

Send the new DSPR pulse immediately after reading

the conversion result to realize maximum throughput.

Sending a new frame sync pulse in the middle of a con-

version immediately aborts the current conversion and

begins a new one. A rising edge on CS in the middle of

a conversion aborts the current conversion and places

the MAX1168 in shutdown.

Output Coding and Transfer Function

The data output from the MAX1167/MAX1168 is straight

binary. Figure 19 shows the nominal transfer function.

Code transitions occur halfway between successive

integer LSB values (V

REF

= +4.096V, and 1 LSB =

+62.5µV or 4.096V / 65,536V).

CS

SCLK

DOUT

I/O

SCK

MISO

SPI

V

DD

SS

MAX1167

MAX1168

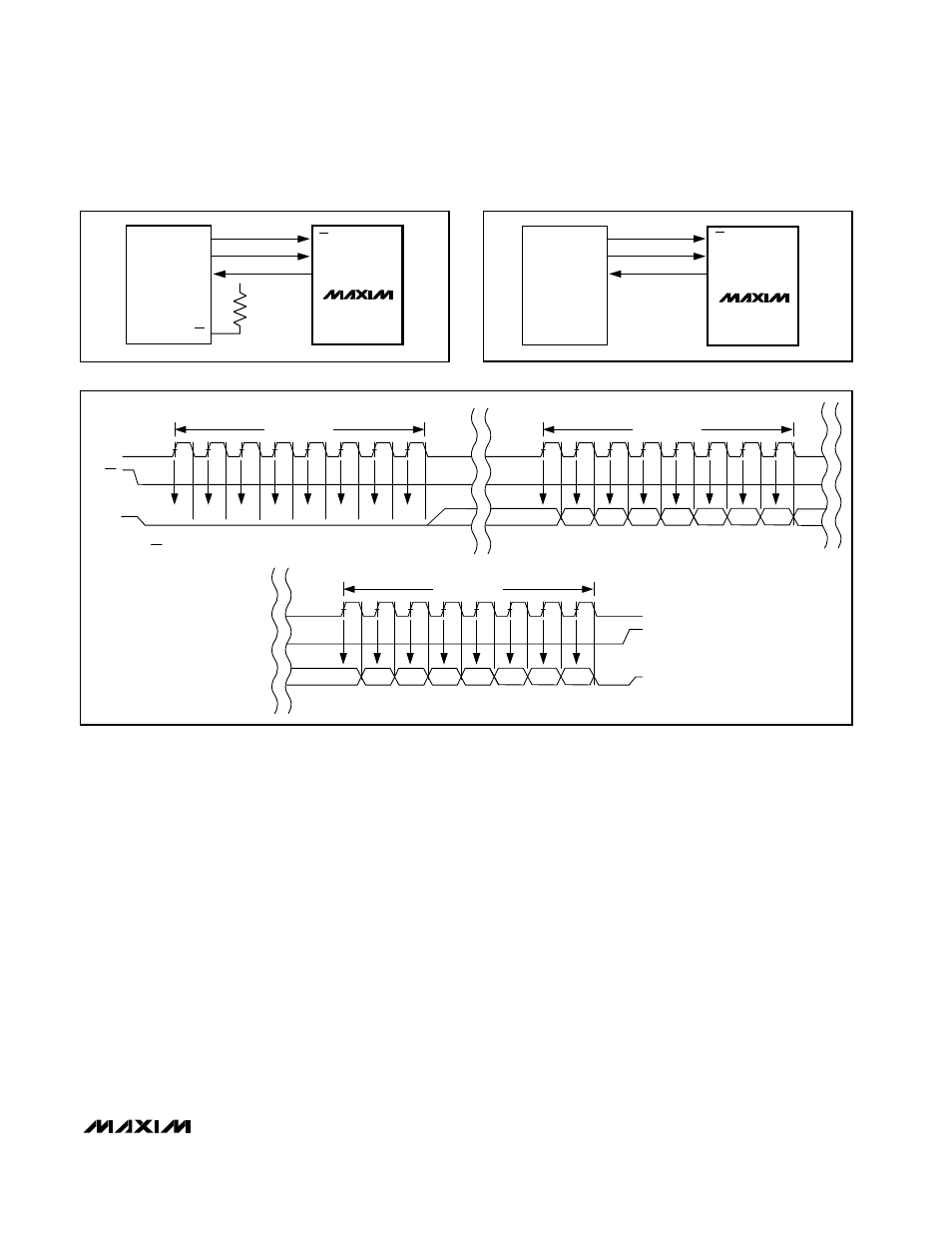

Figure 20a. SPI Connections

MAX1167

MAX1168

CS

MICROWIRE

SCLK

DOUT

I/O

SK

SI

Figure 20b. MICROWIRE Connections

DOUT*

CS

SCLK

1ST BYTE READ

2ND BYTE READ

*WHEN CS IS HIGH, DOUT = HIGH-Z

MSB

HIGH-Z

3RD BYTE READ

LSB

D1

D0

D7

D6

D5

D4

D3

D2

24

20

16

12

8

6

4

1

D15

D14

D13

D12

D11

D10

D9

D8

D7

0

0

0

0

0

0

0

0

Figure 20c. SPI/MICROWIRE Interface Timing Sequence (CPOL = CPHA = 0)