Rainbow Electronics MAX1168 User Manual

Page 20

MAX1167/MAX1168

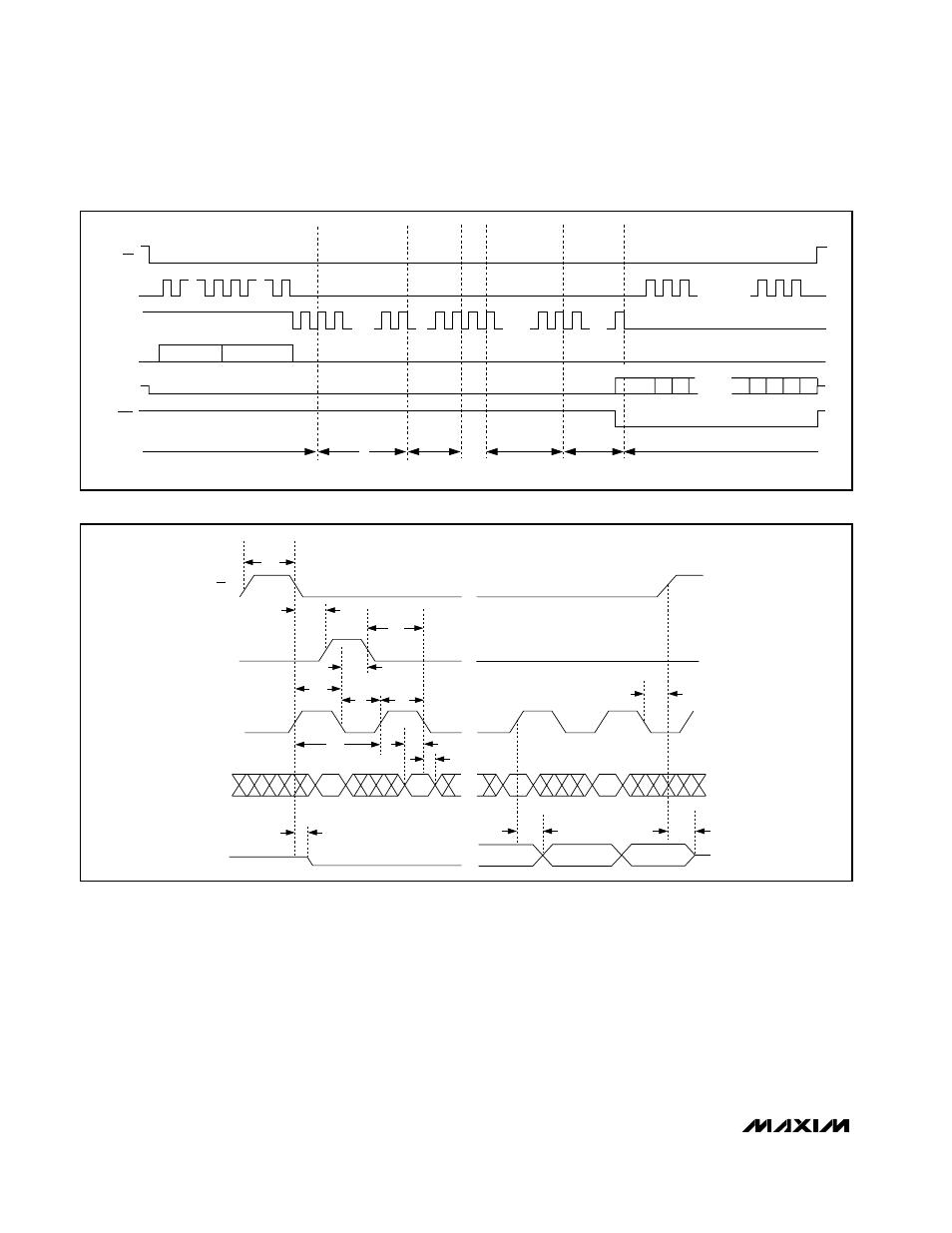

Internal Clock 16-Bit-Wide Data-Transfer and Scan

Mode (MAX1168 Only)

Force DSPR high and DSEL low for the SPI/QSPI/

MICROWIRE interface mode. The falling edge of CS

wakes the analog circuitry and allows SCLK to clock in

data (Figure 13). DOUT changes from high-Z to logic

low after CS is brought low. Input data latches on the

rising edge of SCLK. The command/configuration/con-

trol register begins reading DIN on the first SCLK rising

edge and ends on the rising edge of the 8th SCLK

cycle. The MAX1168 selects the proper channel for

conversion on the rising edge of the 3rd SCLK cycle.

The internal oscillator activates 125ns after the rising

edge of the 16th SCLK cycle. Turn off the external clock

while the internal clock is on. Turning off SCLK ensures

lowest noise performance during acquisition.

Acquisition begins on the 2nd rising edge of the inter-

nal clock and ends on the falling edge of the 18th inter-

nal clock cycle. Each bit of the conversion result shifts

into memory as it becomes available. The conversion

result is available (MSB first) at DOUT on the falling

edge of EOC. The internal oscillator and analog circuitry

Multichannel, 16-Bit, 200ksps Analog-to-Digital

Converters

20

______________________________________________________________________________________

DOUT

CS

SCLK

DIN

EOC

ADC

STATE

INTERNAL

CLK

1

8

9

16

• • •

• • •

• • •

• • •

X = DON

,

T CARE

2

13

17

45

48

64

32

34

• • •

• • •

X X X X X X X X

DATA

LSB

X

• • •

• • •

t

ACQ

POWER-DOWN

t

CONV

t

ACQ

t

CONV

MSB

Figure 15. SPI Internal Clock Mode, 16-Bit Data-Transfer Mode, Scan Mode for Two Conversions, Conversion Timing (MAX1168 Only)

CS

SCLK

DSPR

DIN

DOUT

t

CSS

t

CL

t

DS

t

DH

t

DV

t

CH

t

DO

t

TR

t

FSH

t

CSH

t

DF

t

CP

t

CSW

t

FSS

...

...

...

...

...

Figure 16. Detailed DSP-Interface Timing (MAX1168 Only)