Pin description – Rainbow Electronics MAX8514 User Manual

Page 12

MAX8513/MAX8514

Wide-Input, High-Frequency, Triple-Output Supplies

with Voltage Monitor and Power-On Reset

12

______________________________________________________________________________________

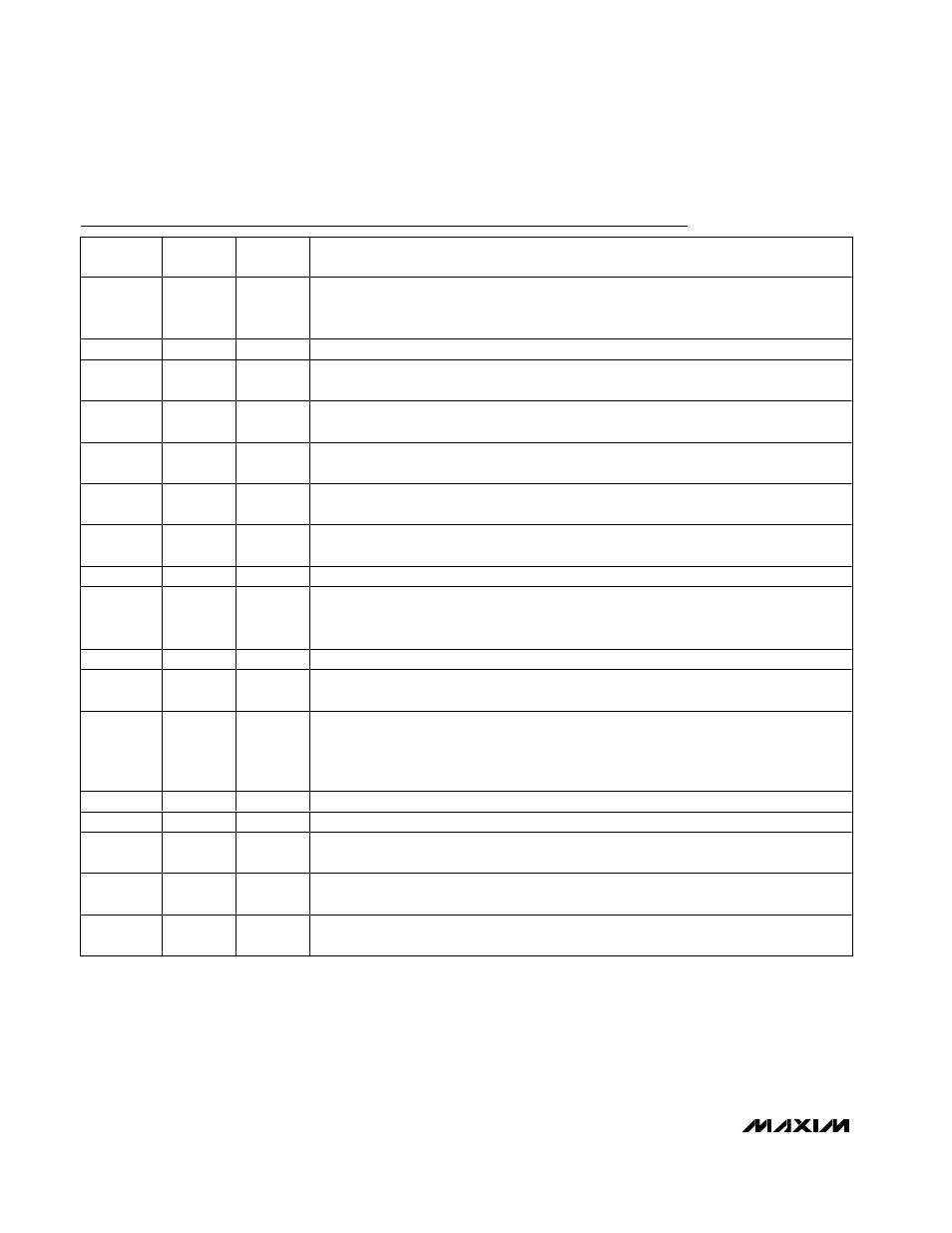

Pin Description

PIN

NAME

MAX8513

MAX8514

FUNCTION

PFI

1

1

Power-Fail Input. Connect PFI to an external resistive-divider between IN, PFI, and GND.

PFI senses V

IN

to detect voltage failure. Trip falling threshold at this input is 1.22V, with

20mV of hysteresis.

PFO

2

2

Power-Fail Output. Open-drain output that goes low if V

PFI

< 1.22V.

DH

3

3

OUT1 High-Side Gate-Drive Output. DH drives the high-side N-channel MOSFET (Q1 in the

Typical Applications Circuits). DH is a floating driver output that swings from LX to BST.

LX

4

4

OUT1 High-Side Driver Return Path. The high-side FET driver uses BST and LX for its

respective high and low-side supplies.

BST

5

5

OUT1 Boost Capacitor Connection for High-Side Gate Drive. Connect a 0.1µF ceramic

capacitor from BST to LX with a less than 5mm trace length.

DL

6

6

OUT1 Low-Side Gate-Drive Output. DL drives the low-side N-channel MOSFET (Q2 in the

Typical Applications Circuits). DL swings from 0 to V

PVL

.

PVL

7

7

OUT1 Gate-Drive Supply Bypass Connection. Connect PVL to VL through a 10

Ω

resistor

(R15), and bypass PVL to PGND with a minimum 1µF capacitor (C1).

PGND

8

8

Power-Ground Connection and Low-Side Supply for Dl Driver

VL

9

9

Internal +5V Linear-Regulator Bypass Pin. Bypass VL to GND with a minimum 2.2µF

ceramic capacitor (C10) and 5mm or less of trace length. VL should be connected to IN

when V

IN

< 5.5V.

COMP1

10

10

OUT1 Compensation Node. See the OUT1 Compensation section.

FB1

11

11

OUT1 Feedback Input. Connect a resistive-divider (R1, R2) from OUT1 to FB1 to GND to

regulate FB1 at 1.25V.

FREQ

12

12

Oscillator Frequency-Set Input. A resistor from FREQ to GND sets the oscillator frequency

from 300kHz to 1.4MHz (f = 15MHz x k

Ω

/ R

FREQ

). R

FREQ

is still required if an external clock

is used at SYNC/EN, and the SYNC/EN input frequency should be within ±30% of the

frequency set by R

FREQ

.

REF

13

13

1.25V Refer ence O utp ut. C onnect a 0.1µF or l ar g er cer am i c cap aci tor ( C 9) fr om RE F to GN D .

GND

14

14

Analog/Signal Ground

FB2

15

15

OUT2 Feedback Input. Connect a resistive-divider (R5, R6) from OUT2 to FB2 to GND to

regulate FB2 to 0.8V.

DRV2

16

16

OUT2 Gate Drive. DRV2 connects to the gate of an external N-channel MOSFET to form a

positive linear voltage regulator.

SUP2

17

17

Supply Input for DRV2. Connect to a voltage source of at least 1V above the maximum

desired DRV2 gate voltage.