Rainbow Electronics MAX5295 User Manual

Page 7

MAX5290–MAX5295

Buffered, Fast-Settling, Dual, 12-/10-/8-Bit,

Voltage-Output DACs

_______________________________________________________________________________________

7

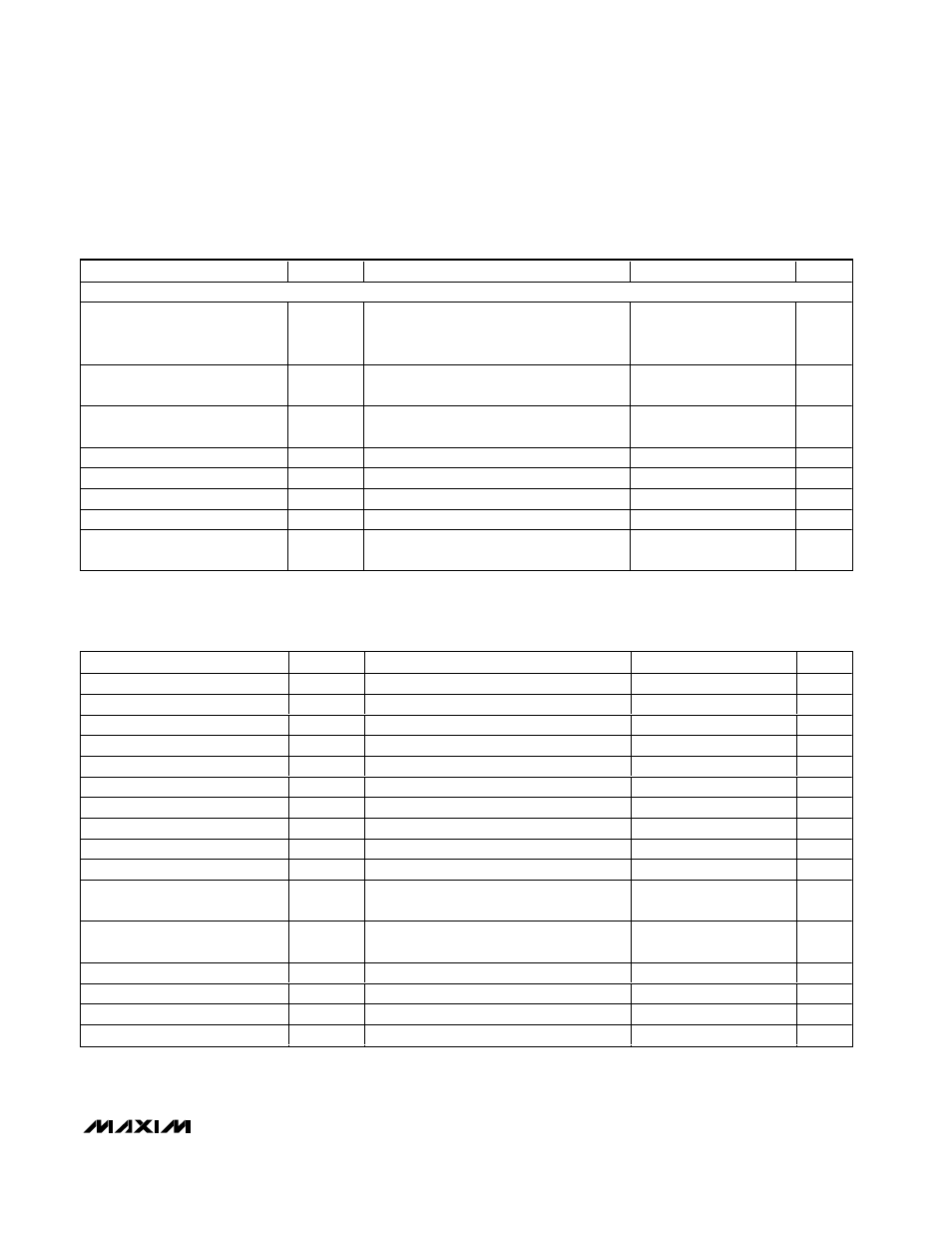

TIMING CHARACTERISTICS—DSP Mode Disabled (1.8V Logic) (Figure 1) (continued)

(DVDD = 1.8V to 3.6V, DGND = 0, TA = TMIN to TMAX, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

UPIO_ TIMING CHARACTERISTICS

DOUT Tri-State Time when

Exiting DOUTDC0, DOUTDC1, or

DOUTRB UPIO Modes

t

DOZ

C

L

= 20pF, from end of write cycle to UPIO_

in high impedance

200

ns

DOUTRB Tri-State Time from CS

Rise

t

DRBZ

C

L

= 20pF, from rising edge of CS to UPIO_

in high impedance

40

ns

DOUTRB Tri-State Enable Time

from 8th SCLK Rise

t

ZEN

C

L

= 20pF, from 8th rising edge of SCLK to

UPIO_ driven out of tri-state

40

ns

LDAC Pulse-Width Low

t

LDL

Figure 5

40

ns

LDAC Effective Delay

t

LDS

Figure 6

200

ns

CLR, MID, SET Pulse-Width Low

t

CMS

Figure 5

40

ns

GPO Output Settling Time

t

GP

Figure 6

200

ns

GPO Output High-Impedance

Time

t

GPZ

200

ns

TIMING CHARACTERISTICS—DSP Mode Enabled (3V, 3.3V Logic) (Figure 2)

(DVDD = 2.7V to 3.6V, DGND = 0, TA = TMIN to TMAX, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SCLK Frequency

f

SCLK

2.7V < DV

DD

< 3.6V

20

MHz

SCLK Pulse-Width High

t

CH

(Note 7)

20

ns

SCLK Pulse-Width Low

t

CL

(Note 7)

20

ns

CS Fall to SCLK Fall Setup Time

t

CSS

10

ns

DSP Fall to SCLK Fall Setup Time

t

DSS

10

ns

SCLK Fall to CS Rise Hold Time

t

CSH

5

ns

SCLK Fall to CS Fall Delay

t

CS0

10

ns

SCLK Fall to DSP Fall Delay

t

DS0

10

ns

DIN to SCLK Fall Setup Time

t

DS

12

ns

DIN to SCLK Fall Hold Time

t

DH

5

ns

SCLK Rise to DOUT_ Valid

Propagation Delay

t

DO1

C

L

= 20pF, UPIO_ = DOUTDC1 or DOUTRB

mode

30

ns

SCLK Fall to DOUTDC0 Valid

Propagation Delay

t

DO2

C

L

= 20pF, UPIO_ = DOUTDC0 mode

30

ns

CS Rise to SCLK Fall Hold Time

t

CS1

MICROWIRE and SPI modes 0 and 3

10

ns

CS Pulse-Width High

t

CSW

45

ns

DSP Pulse-Width High

t

DSW

20

ns

DSP Pulse-Width Low

t

DSPWL

(Note 8)

20

ns