Applications information – Rainbow Electronics MAX9671 User Manual

Page 21

MAX9670/MAX9671

Low-Power Audio/Video Switch with Audio

Volume Control for Dual SCART Connectors

______________________________________________________________________________________

21

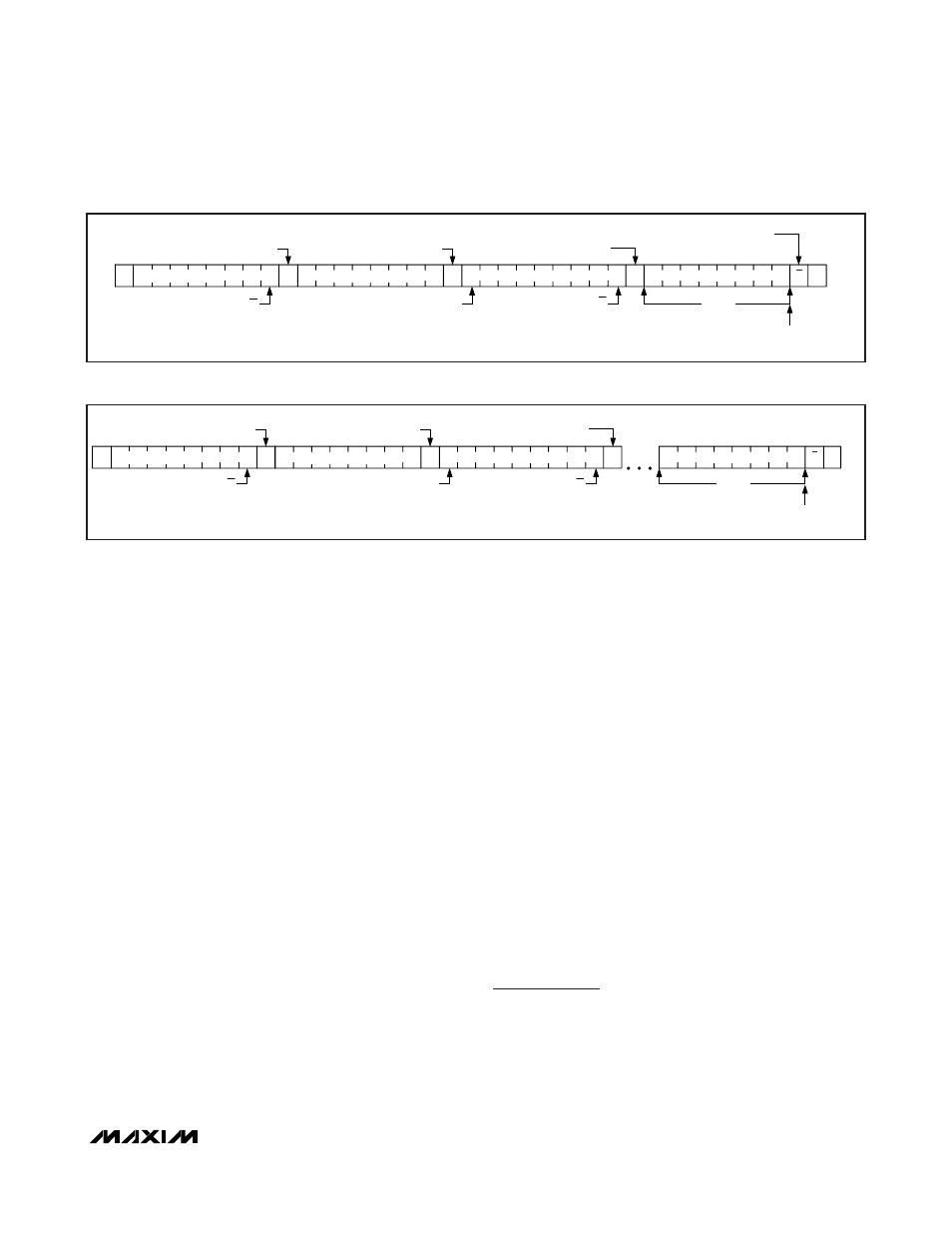

The third byte sent to the MAX9670/MAX9671 contains

the data that is written to the chosen register. An

acknowledge pulse from the MAX9670/MAX9671 sig-

nals receipt of the data byte. The address pointer

autoincrements to the next register address after each

received data byte. This autoincrement feature allows a

master to write to sequential register address locations

within one continuous frame. The master signals the

end of transmission by issuing a STOP (P) condition.

Read Data Format

The master presets the address pointer by first sending

the MAX9670/MAX9671’s slave address with the R/W

bit set to 0 followed by the register address after a

START (S) condition. The MAX9670/MAX9671 acknowl-

edges receipt of its slave address and the register

address by pulling SDA low during the ninth SCL clock

pulse. A REPEATED START (Sr) condition is then sent

followed by the slave address with the R/W bit set to 1.

The MAX9670/MAX9671 transmits the contents of the

specified register. Transmitted data is valid on the ris-

ing edge of the master-generated serial clock (SCL).

The address pointer autoincrements after each read

data byte. This autoincrement feature allows all regis-

ters to be read sequentially within one continuous

frame. A STOP condition can be issued after any num-

ber of read data bytes. If a STOP condition is issued

followed by another read operation, the first data byte

to be read is from the register address location set by

the previous transaction and not 00h and subsequent

reads autoincrement the address pointer until the next

STOP condition. Attempting to read from register

addresses higher than 01h results in repeated reads

from a dummy register containing FFh data. The master

acknowledges receipt of each read byte during the

acknowledge clock pulse. The master must acknowl-

edge all correctly received bytes except the last byte.

The final byte must be followed by a not acknowledge

from the master and then a STOP condition. Figures 11

and 12 illustrate the frame format for reading data from

the MAX9670/MAX9671.

Interrupt Output

When interrupt is enabled in modes 1 and 2, INT, which

is an open-drain output, pulls low under the following

conditions: slow-switch signals change value, CVBS

input signals are detected or disappear, and CVBS out-

put loads are added or removed.

When interrupt is enabled in mode 3, INT pulls low only

when the slow-switch signal changes value.

Enable INT by writing a 1 into bit 4 of register 01h. See

Table 13.

The interrupt can be cleared by reading register 0Eh

and 0Fh.

Applications Information

Audio Inputs

The maximum full-scale audio signal that can be

applied to the audio inputs is 0.5V

RMS

biased at

ground. The recommended application circuit to atten-

uate and bias an incoming audio signal is shown in

Figure 13.

ACKNOWLEDGE FROM

MAX9670/MAX9671

1 BYTE

AUTOINCREMENT INTERNAL

REGISTER ADDRESS POINTER

ACKNOWLEDGE FROM

MAX9670/MAX9671

NOT ACKNOWLEDGE FROM MASTER

A

A

P

A

0

ACKNOWLEDGE FROM

MAX9670/MAX9671

R/W

S

A

R/W

REPEATED START

Sr

1

SLAVE ADDRESS

REGISTER ADDRESS

SLAVE ADDRESS

DATA BYTE

Figure 11. Reading One Indexed Byte of Data from the MAX9670/MAX9671

ACKNOWLEDGE FROM

MAX9670/MAX9671

1 BYTE

AUTOINCREMENT INTERNAL

REGISTER ADDRESS POINTER

ACKNOWLEDGE FROM

MAX9670/MAX9671

A

A

A

P

0

ACKNOWLEDGE FROM

MAX9670/MAX9671

R/W

S

A

R/W

REPEATED START

Sr

1

SLAVE ADDRESS

REGISTER ADDRESS

SLAVE ADDRESS

DATA BYTE

Figure 12. Reading n Bytes of Indexed Data from the MAX9670/MAX9671