Ethernet avb endpoint address space, Table 10-1, Tx ptp packet control register – Xilinx IP Ethernet AVB Endpoint v2.4 UG492 User Manual

Page 92: Is defined, Rx ptp packet buffer address space, Tx ptp packet buffer address space

92

Ethernet AVB Endpoint User Guide

UG492 September 21, 2010

Chapter 10: Configuration and Status

Ethernet AVB Endpoint Address Space

Rx PTP Packet Buffer Address Space

The Address space of the

is 4k bytes, from PLB_base_address to

(PLB_base_address + 0x0FFF). This represents the size of a single Virtex®-5 FPGA block

RAM pair (4k bytes). Every byte of this Block RAM can be read from the PLB. See

for operation.

Tx PTP Packet Buffer Address Space

The Address space of the

is continuous from (PLB_base_address +

0x1000) to (PLB_base_address + 0x17FF), representing the size of a single Virtex-5 FPGA

Block 18k RAM (2k bytes). Every byte of this Block RAM is read/write accessible via the

PLB. See

for operation.

Ethernet Audio Video End Point Configuration Registers

Tx PTP Packet Control Register

defines the associated control register of the

used by the

to request the transmission of the PTP frames.

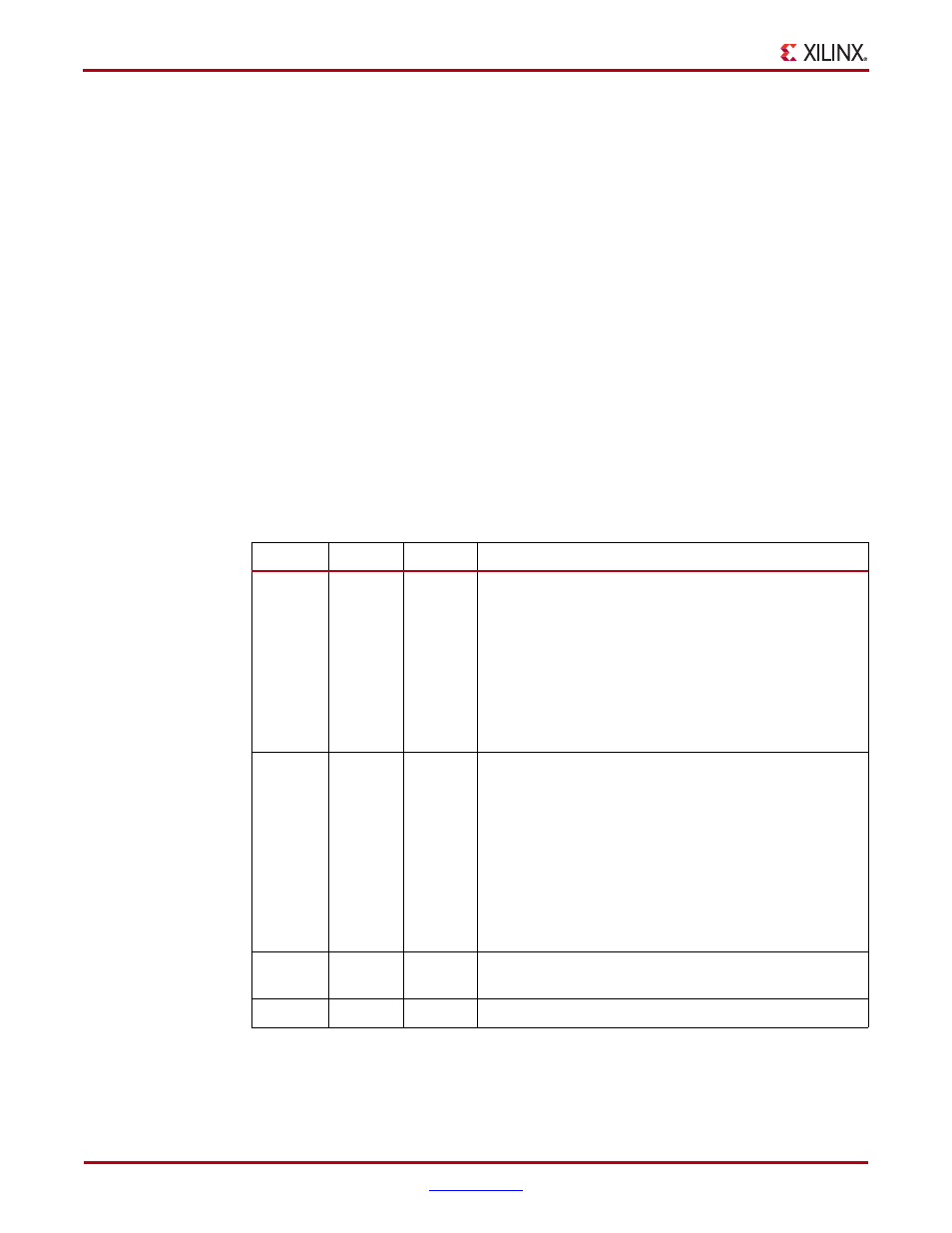

Table 10-1:

Tx PTP Packet Buffer Control Register (PLB_base_address + 0x2000)

Bit no

Default

Access

Description

7-0

0

WO

tx_send_frame

bits. The Tx PTP Packet Buffer is split into

8 regions of 256 bytes. Each of these can contain a separate

PTP frame. There is 1 tx_send_frame bit for each of the 8

regions.

Each bit, when written to ‘1’, will cause a request to be

made to the

When access is granted, the

frame contained within the respected region will be

transmitted.

If read, will always return 0.

15-8

0

RO

tx_frame_waiting

indication. The Tx PTP Packet Buffer is

split into 8 regions of 256 bytes, each of which can contain

a separate PTP frame. There is 1 tx_frame_waiting bit for

each of the 8 regions.

Each bit, when logic 1, indicates that a request has been

made for frame transmission to the

but that

a grant has not yet occurred. When the frame has been

successfully transmitted, the bit will be set to logic 0.

This bit allows the microprocessor to run off a polling

implementation as opposed to the Interrupts.

18-16

0

RO

tx_packet

. indicates the number (block RAM bin position)

of the most recently transmitted PTP packet.

31-19

0

RO

Unused

Note:

A read or a write to this register clears the interrupt_ptp_tx interrupt (asserted after each

successful PTP packet transmission).