Figure 14-1 – Xilinx IP Ethernet AVB Endpoint v2.4 UG492 User Manual

Page 138

138

Ethernet AVB Endpoint User Guide

UG492 September 21, 2010

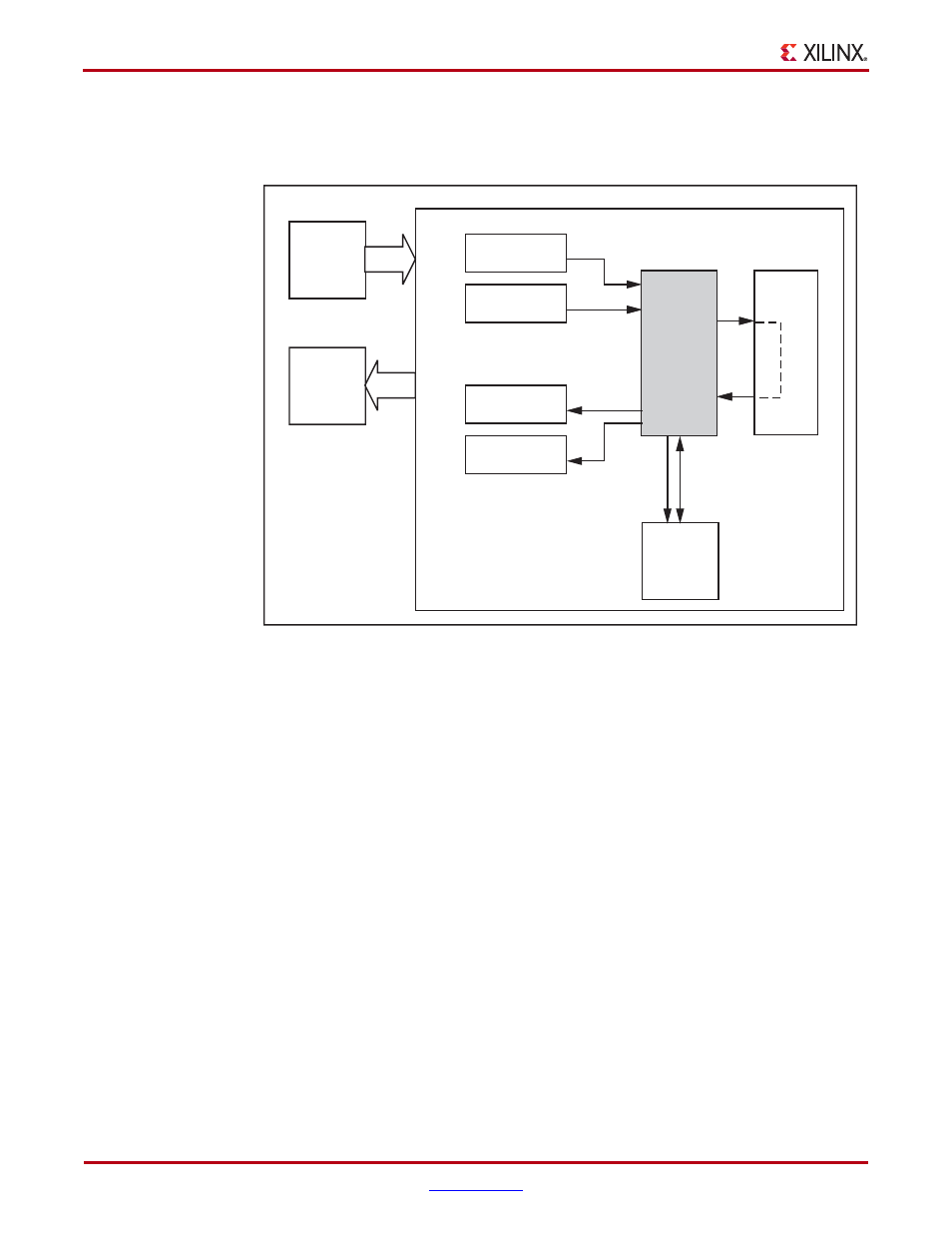

Chapter 14: Quick Start Example Design

The Ethernet AVB Endpoint example design has been tested using Xilinx® ISE® software

v12.2, Cadence Incisive Enterprise Simulator (IES) v9.2, Mentor Graphics ModelSim v 6.5c,

and Synopsys VCS and VCS MX 2009.12.

X-Ref Target - Figure 14-1

Figure 14-1:

Ethernet AVB Endpoint Example Design and Test Bench

Example Design Top Level

Ethernet

AVB

Endpoint

LogiCORE

legacy

traffic

AV traffic

Tx frame

stimulus

loopback

module

Tx frame

stimulus

Rx frame

checker

Rx frame

checker

PLB

Interrupts

PLB

module

AV traffic

legacy

traffic

Clock

and

Reset

generation

Statistic

Gathering

Demonstration Test Bench