Simulation/timing, Table 15-9 – Xilinx IP Ethernet AVB Endpoint v2.4 UG492 User Manual

Page 148

148

Ethernet AVB Endpoint User Guide

UG492 September 21, 2010

Chapter 15: Detailed Example Design (Standard Format)

simulation/timing

The timing directory contains timing simulation scripts provided with the core.

wave_ncsim.sv

IES macro file that opens a wave window and

adds signals of interest to it. It is called by the

simulate_ncsim.sh

script file.

simulate_vcs.sh

VCS script file that compiles the Verilog

sources and runs the functional simulation to

completion.

vcs_commands.key

This file is sourced by VCS at the start of

simulation; it configures the simulator.

vcs_session.tcl

VCS macro file that opens a wave window

and adds signals of interest to it. It is called by

the simulate_vcs.sh script file.

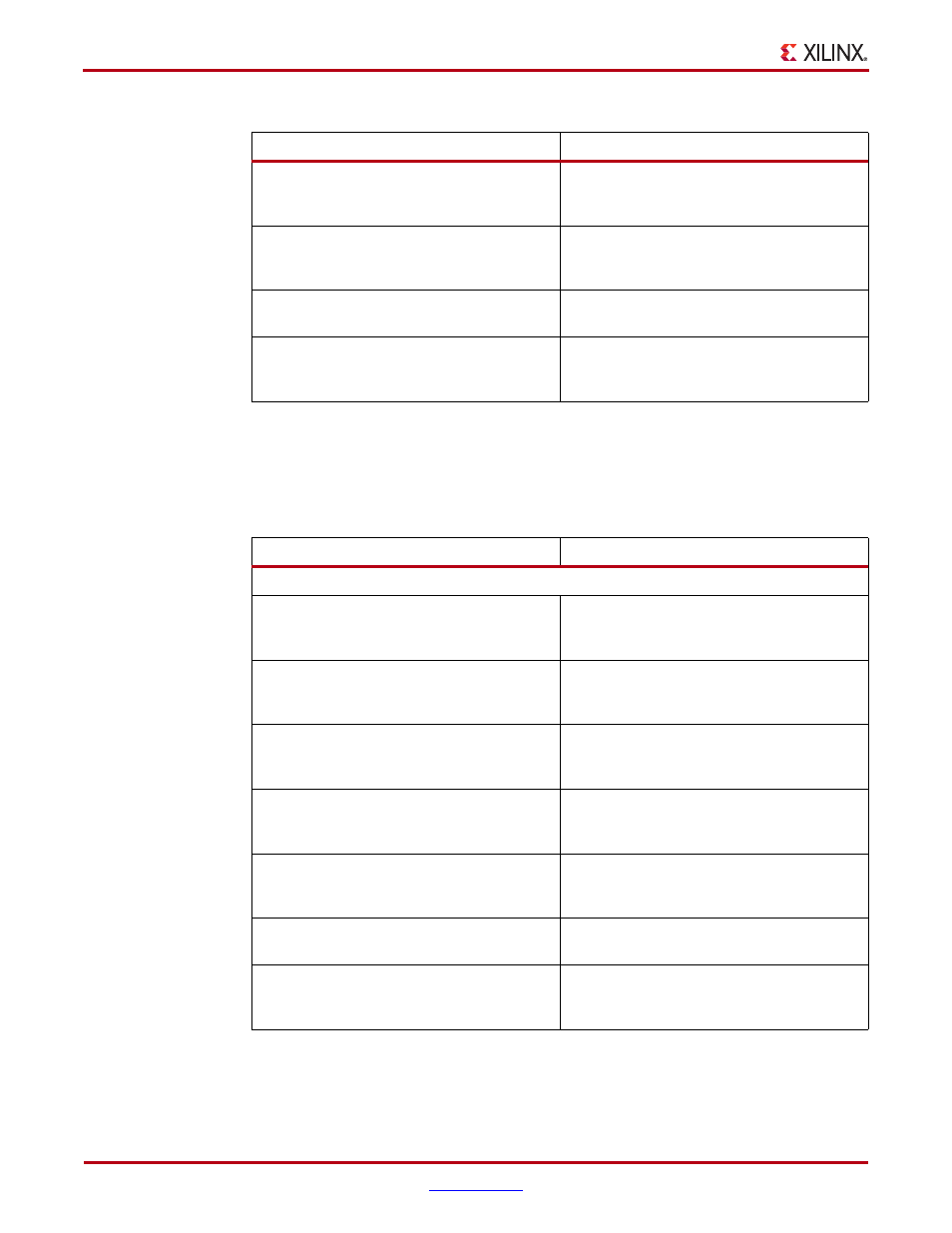

Table 15-8:

Functional Directory (Cont’d)

Name

Description

Table 15-9:

Timing Directory

Name

Description

simulate_mti.do

ModelSim macro file that compiles Verilog or

VHDL sources and runs the timing

simulation to completion.

wave_mti.do

ModelSim macro file that opens a wave

window and adds signals of interest to it. It is

called by the simulate_mti.do macro file.

simulate_ncsim.sh

IES script file that compiles the Verilog or

VHDL sources and runs the timing

simulation to completion.

wave_ncsim.sv

IES macro file that opens a wave window and

adds signals of interest to it. It is called by the

simulate_ncsim.sh

script file.

simulate_vcs.sh

VCS script file that compiles the Verilog

sources and runs the timing simulation to

completion.

vcs_commands.key

File sourced by VCS at the start of simulation;

it configures the simulator.

vcs_session.tcl

VCS macro file that opens a wave window

and adds signals of interest to it. It is called by

the simulate_vcs.sh script file.