Table 5-7, Table 5-8, Mac receiver interface – Xilinx IP Ethernet AVB Endpoint v2.4 UG492 User Manual

Page 51: Mac management interface

Ethernet AVB Endpoint User Guide

51

UG492 September 21, 2010

Core Interfaces

MAC Receiver Interface

These signals connect directly to the identically named Tri-Mode Ethernet MAC signals

and are synchronous to rx_clk

MAC Management Interface

This interface is only present when the core is generated in

, designed for connection to LogiCORE IP Tri-Mode Ethernet MAC devices.

When present, these signals connect directly to the identically named LogiCORE IP Tri-

Mode Ethernet MAC signals (except where stated in

) and are synchronous to

host_clk

. When present, all MAC configuration and MDIO register space is address

mapped into the PLB of the Ethernet AVB Endpoint core. A logic shim automatically drives

this interface to access the MAC when the appropriate PLB address space is accessed.

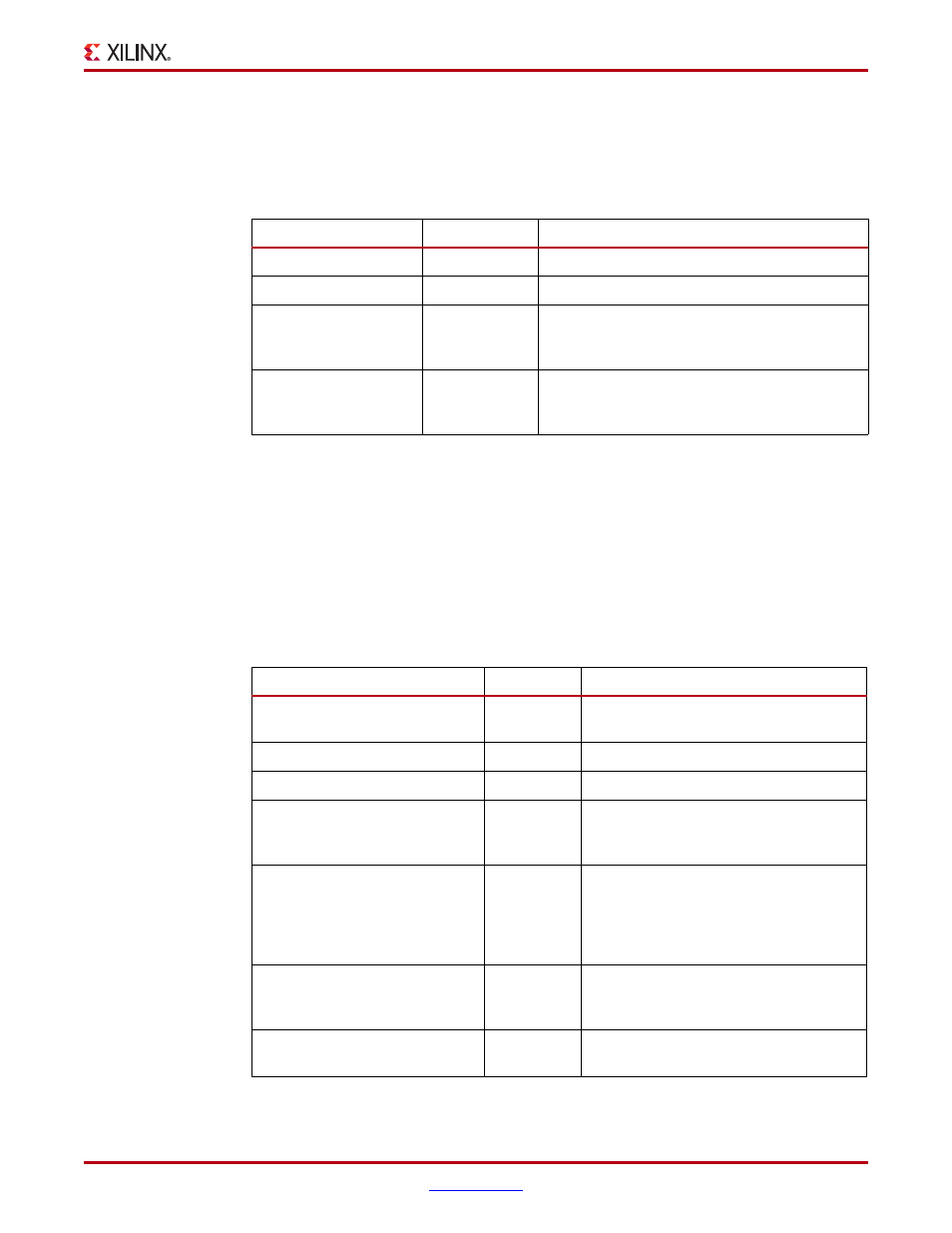

Table 5-7:

Tri-Mode Ethernet MAC Receiver Interface

Signal

Direction

Description

rx_data[7:0]

Input

Frame data received is supplied on this port.

rx_data_valid

Input

Control signal for the rx_data[7:0] port

rx_frame_good

Input

Asserted at the end of frame reception to indicate

that the frame should be processed by the

Ethernet AVB Endpoint core.

rx_frame_bad

Input

Asserted at the end of frame reception to indicate

that the frame should be discarded by the MAC

client.

Table 5-8:

Tri-Mode Ethernet MAC Host Interface (Configuration/Status)

Signal

Direction

Description

host_opcode[1:0]

Output

Defines the MAC operation

(configuration or MDIO, read or write)

host_addr[9:0]

Output

Address of the MAC register to access

host_wr_data[31:0]

Output

Data to be written to the MAC register

host_rd_data_mac[31:0]

Input

Data read from the MAC register (connect

to the host_rd_data[31:0] signal of the

MAC)

host_rd_data_stats[31:0]

Input

Data read from the Ethernet Statistics core

(connect to the host_rd_data[31:0] signal

of the Ethernet Statistics core, if present).

If the statistics core is not used, then

connect to logic 0.

host_miim_sel

Output

When asserted, the MAC will access the

MDIO port, when not asserted, the MAC

will access configuration registers

host_req

Output

Used to initiate a transaction onto the

MDIO