Texas Instruments THUNDER TNETX3270 User Manual

Page 57

TNETX3270

ThunderSWITCH

24/3 ETHERNET

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

57

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

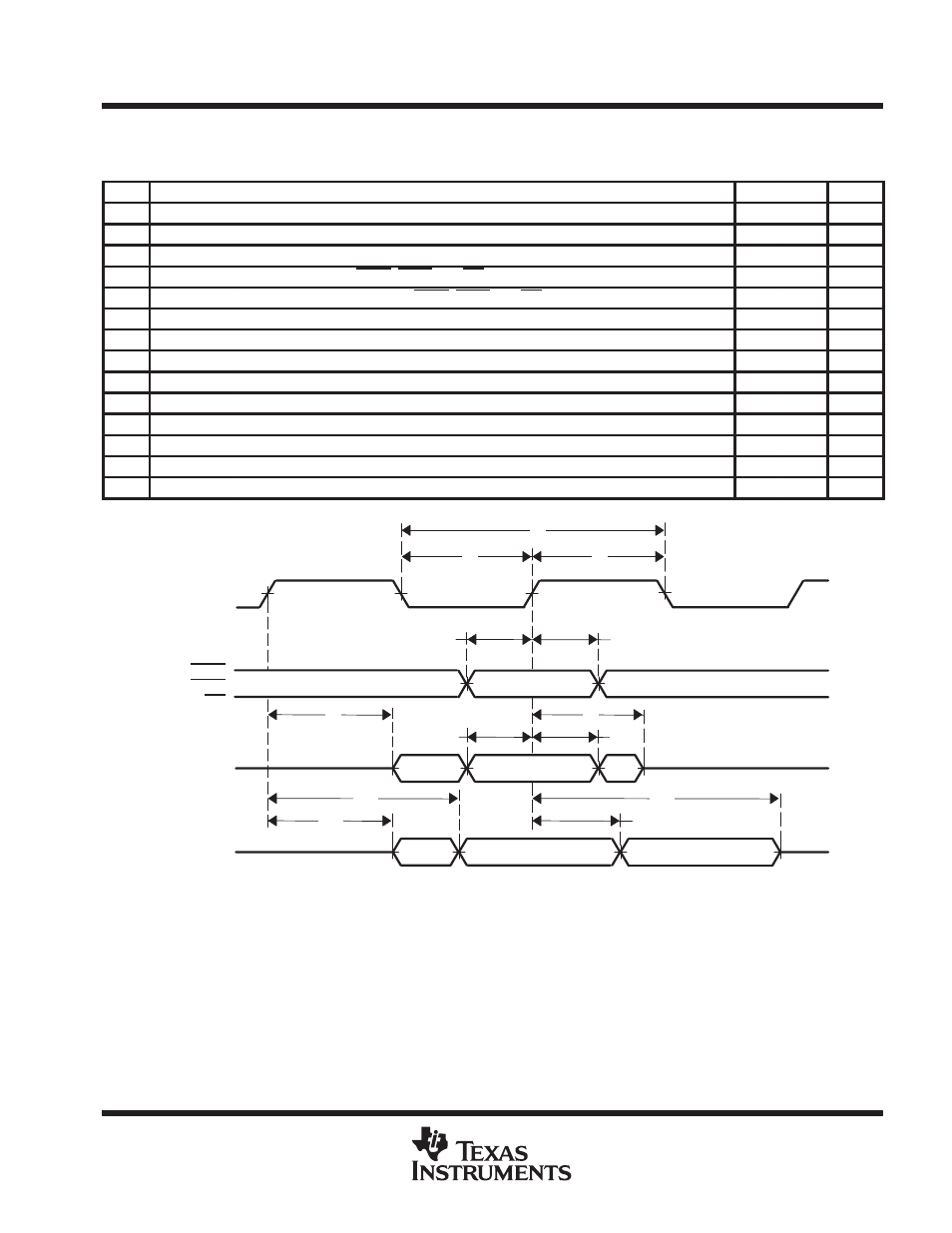

SDRAM subcycle

operating characteristics over recommended operating conditions (see Figure 17)

NO.

PARAMETER

MIN

MAX

UNIT

1

tc(DCLK)

Cycle time, DCLK

12

12

ns

2

tw(DCLKL)

Pulse duration, DCLK low

5

ns

3

tw(DCLKH)

Pulse duration, DCLK high

5

ns

4

td(DCLK)

Delay time, from DA, DRAS, DCAS, and DW valid to DCLK

↑

4

ns

5

td(DA)

Delay time, from DCLK

↑

to DA, DRAS, DCAS, and DW invalid

2

ns

6

ten(DDW)

Enable time, from DCLK

↑

to before DD31–DD00 driven (write cycle)

0

ns

7

ten(DDR)

Enable time, from DCLK

↑

to before DD31–DD00 driven (read cycle)

0

ns

8

tdis(DDW)

Disable time, from DCLK

↑

to after DD31–DD00 (after final write cycle) to Z state

10

ns

9

tdis(DDR)

Disable time, from DCLK

↑

to after DD31–DD00 (after final read cycle) to Z state

11

ns

10

td(DDW)1

Delay time, from DD valid to DCLK

↑

(write cycle)

4

ns

11

td(DDW)2

Delay time, from DCLK

↑

to DD31–DD00 Z state (write cycle)

2

ns

12

td(DDR)1

Delay time, from DCLK

↑

to DD31–DD00 valid (read cycle)

10

ns

13

td(DDR)2

Delay time, from DCLK

↑

to DD31–DD00 invalid (read cycle)

0

ns

tt

Transition time, rise and fall, all signals

1

4

ns

ООООООО

ООООООО

О

О

ОО

ОО

О

О

ОООО

ОООО

ООООООООООО

ООООООООООО

ОООООООООО

ОООООООООО

DCLK

(output)

1

DA13–DA00

DRAS

DCAS

DW

(outputs)

DD31–DD00

(during writes)

(output)

ОООО

ОООО

DD31–DD00

(during reads)

(input)

Z

Z

Z

Z

2

3

4

5

6

10

8

11

12

9

13

7

Figure 17. SDRAM Subcycle