/100-mbit/s mac interface, /100-mbit/s – Texas Instruments THUNDER TNETX3270 User Manual

Page 54

TNETX3270

ThunderSWITCH

24/3 ETHERNET

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

54

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

THxCLK

(input)

THxSYNC

(input)

THxCOL

THxCRS

THxLINK

THxRXD3–THxRXD0

THxRXDV

(inputs)

THxTXEN

THxTXD3–THxTXD0

THxRENEG

(outputs)

1

2

2

5

3

6

4

8

7

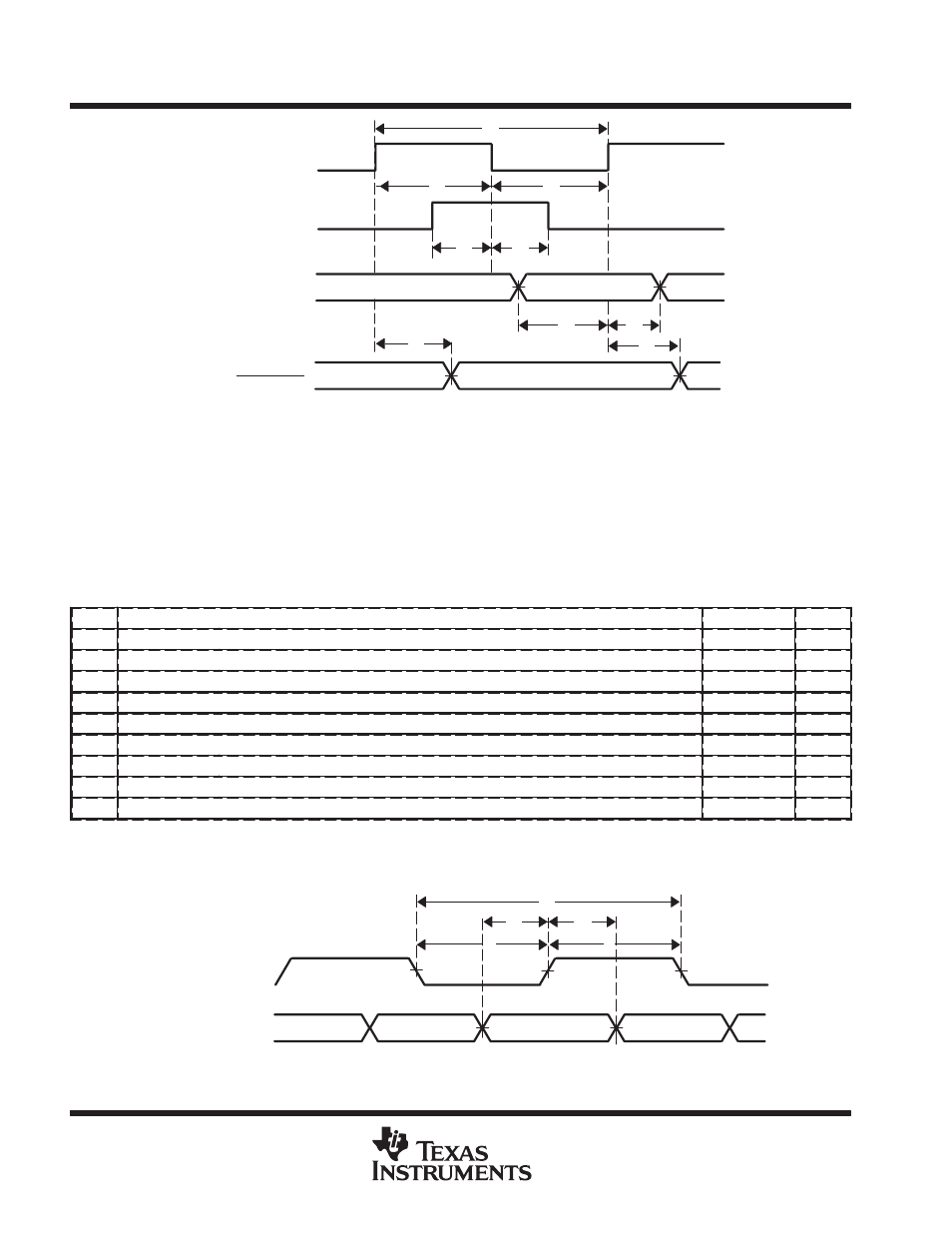

Figure 13. 10-Mbit/s Interface (Ports 00–23)

10-/100-Mbit/s MAC interface

Figures 14 and 15 show the timings at 100 Mbit/s and 10 Mbit/s for the 10-/100-Mbit/s port interfaces to the

TNETE2101 devices.

10-/100-Mbit/s

receive ports (24, 25, 26)

timing requirements (see Note 7 and Figure 14)

NO.

MIN

MAX

UNIT

1

tc(MxxRCLK)

Cycle time, MxxRCLK

25

25

ns

2

tw(MxxRCLKL)

Pulse duration, MxxRCLK low

ns

3

tw(MxxRCLKH)

Pulse duration, MxxRCLK high

14

ns

4†

tsu(MxxRXD)

Setup time, MxxRXD3–MxxRXD0 valid before MxxRCLK

↑

5

ns

4†

tsu(MxxRXDV)

Setup time, MxxRXDV valid before MxxRCLK

↑

5

ns

4†

tsu(MxxRXER)

Setup time, MxxRXER valid before MxxRCLK

↑

5

ns

5†

th(MxxRXD)

Hold time, MxxRXD3–MxxRXD0 valid after MxxRCLK

↑

5

ns

5†

th(MxxRXDV)

Hold time, MxxRXDV valid after MxxRCLK

↑

5

ns

5†

th(MxxRXER)

Hold time, MxxRXER valid after MxxRCLK

↑

5

ns

† xx = ports 24, 25, and 26

NOTE 7: Both MxxCRS and MxxCOL are driven asynchronously by the PHY. MxxRXD3–MxxRXD0 is driven by the PHY on the falling edge of

MxxRCLK. MxxRXD3–MxxRXD0 timing must be met during clock periods when MxxRXDV is asserted. MxxRXDV is asserted and

deasserted by the PHY on the falling edge of MxxRCLK. MxxRXER is driven by the PHY on the falling edge of MxxRCLK.

ОООООО

ОООООО

ОООООО

ОООООО

MxxRXD3–MxxRXD0

MxxRXDV

MxxRXER

(inputs)

MxxRCLK

(input)

4

5

1

2

2

Figure 14. 10-/100-Mbit/s Receive Ports