Texas Instruments THUNDER TNETX3270 User Manual

Page 29

TNETX3270

ThunderSWITCH

24/3 ETHERNET

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

29

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

JTAG interface

The TNETX3270 is fully IEEE Std 1149.1 compliant. It also includes on-chip pullup resistors on the five JTAG

terminals to eliminate the need for external ones. All JTAG inputs and outputs are 3.3-V tolerant.

The following instructions are supported:

D

EXTEST, BYPASS, and SAMPLE/PRELOAD

D

HIGHZ and IDCODE

D

Private (various private instructions are used by TI for test purposes)

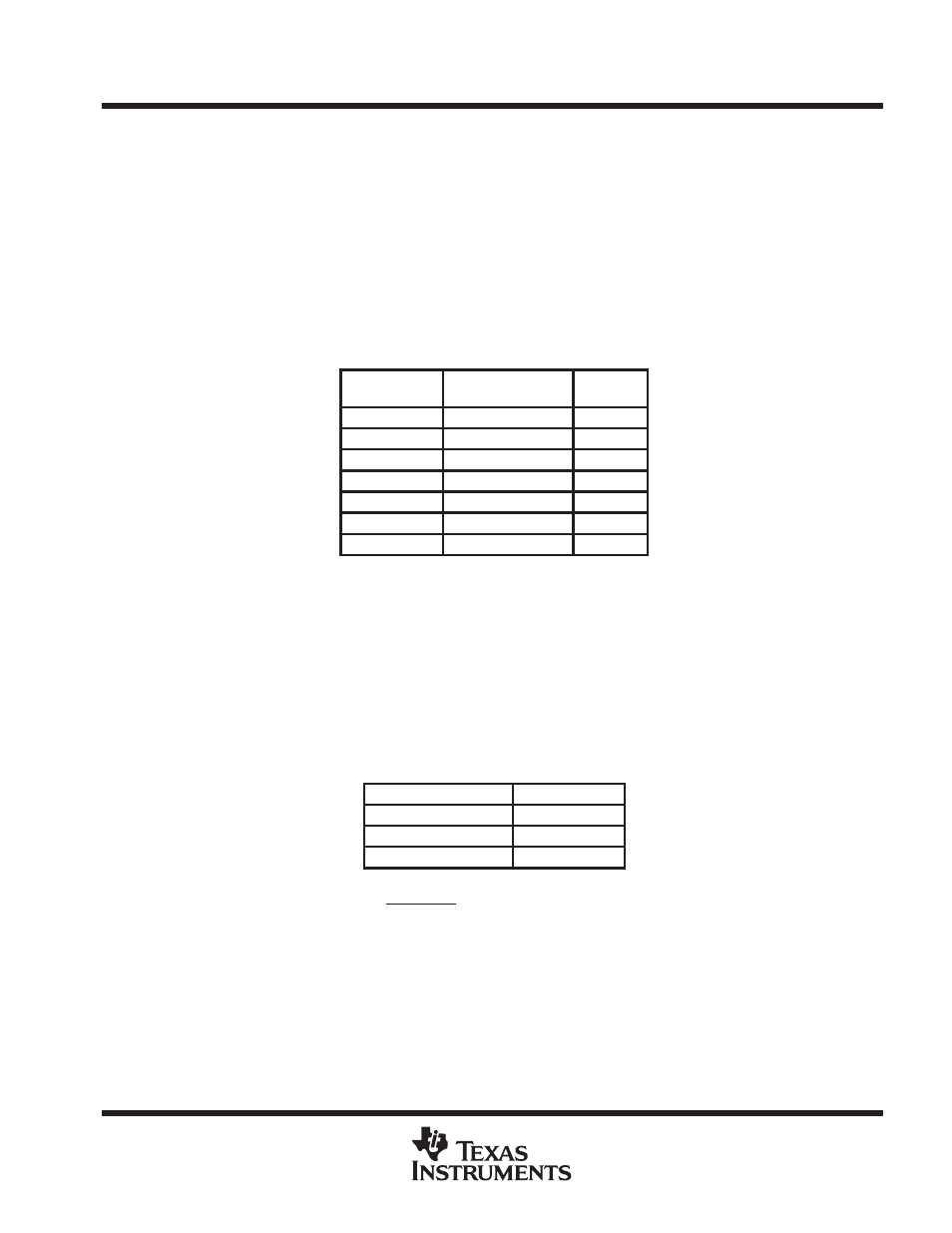

The opcodes for the various instructions (6-bit instruction register) are shown in Table 8.

Table 8. JTAG Instruction Opcodes

INSTRUCTION

TYPE

INSTRUCTION

NAME

JTAG

OPCODE

Mandatory

EXTEST

000000

Mandatory

SAMPLE/PRELOAD

000001

Optional

IDCODE

000100

Optional

HIGHZ

000101

Optional

RACBIST

000110

Private

TI testing

Others

Mandatory

BYPASS

111111

HIGHZ instruction

When selected, the HIGHZ instruction causes all outputs and bidirectional pins to become high impedance. All

pullup and pulldown resistors are disabled.

LED interface

This interface allows a visual status for each port to be displayed. In addition, the state of the internal flow control

and fault functions are displayed along with 12 software-controllable LEDs.

Each port has a single LED, which can convey three states (see Table 9).

Table 9. LED States

STATE

DISPLAY

No link

Off

Link, but no activity

On

Activity (bits moving)

Flashing at 8 Hz

The interface is intended for use with external octal shift registers clocked with LEDCLK. Every 16th of a second,

all the status bits are shifted out via LEDDATA.

The status bits are shifted out in one of two possible orders, as determined by slast in LEDControl, to ensure

that systems that do not require all the LED status can be implemented with the minimum number of octal shift

registers (see Table 10).

D

If slast = 0, the software-controlled status bits are shifted out before the port status bits.

D

If slast = 1, the software-controlled status bits are shifted out after the port status bits.

The fault status bit is shifted out last, enabling a minimal system that displays only the fault status to be

implemented without any shift registers.