Sdram interface – Texas Instruments THUNDER TNETX3270 User Manual

Page 56

TNETX3270

ThunderSWITCH

24/3 ETHERNET

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

56

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

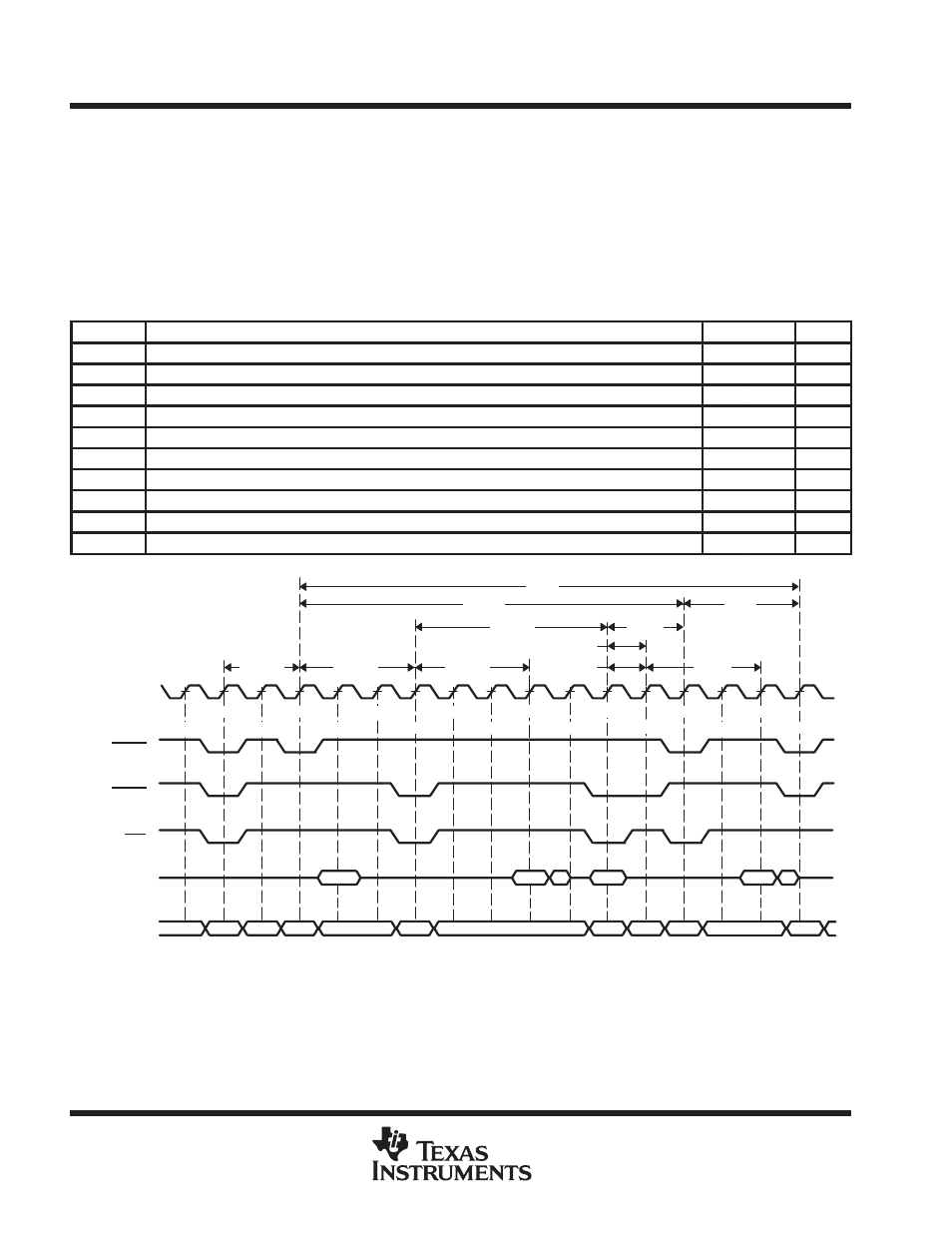

SDRAM interface

The SDRAM interface observes two types of timing:

D

Multicycle timings between commands

D

Subcycle timings between signals and DCLK

Figure 16 illustrates the SDRAM interfaces signal timing in which each type of SDRAM command and its

interrelated timings are shown. It is not intended to be representative of any particular receive or transmit buffer

operation.

SDRAM command to command (see Figure 16)

SYMBOL

PARAMETER

MIN

MAX

UNIT

tRSA

MRS to ACTV or REFR

24

ns

tRC

Row cycle time (ACTV to REFR to next ACTV or REFR)

120

ns

tRAS

Row active time (ACTV to DCAB)

72

ns

tRP

Row recharge time (DCAB to ACTV, REFR, or MRS)

36

ns

tRCD

Row to column delay (ACTV to READ or WRT)

36

ns

tAC3

Column access time [READ (CAS) latency] (READ to data sample)

36

ns

nCCD

Column address to column address (WRT to next READ or WRT, or READ to next READ)

24

ns

nCWL

Last data or write to new column address (WRT to next READ or WRT)

24

ns

tRWD

Read to write delay (READ to next WRT)

60

ns

tWR

Write recovery time (WRT to DCAB)

24

ns

О

О

ООО

ООО

ОООО

ОООО

ОООО

ОООО

ООООООО

ООООООО

ООО

ООО

ОО

ОО

ОО

ОО

О

О

DCLK

tRC

tRP

tRWD

tWR

nCWL

nCCD

tRCD

tRAS

tRSA

tAC3

tAC3

DRAS

DCAS

DW

DD31–DD00

DA13–DA00

REGISTER

SETTINGS

BUFFOP

READ1

WRITE

READ2

MODE

ROW

READ1

WRITE

READ2

XXXX

DA10=0

DA10=0

DA10=1

DA10=0

NOOP

NOOP

ACTV

READ

READ

DCAB

REFR

NOOP

NOOP

NOOP

NOOP

NOOP

NOOP

WRT

NOOP

NOOP

MRS

Figure 16. SDRAM Command to Command