/100-mbit/s, Timing requirements (see figure 15) – Texas Instruments THUNDER TNETX3270 User Manual

Page 55

TNETX3270

ThunderSWITCH

24/3 ETHERNET

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

55

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

10-/100-Mbit/s

transmit ports (24, 25, and 26)

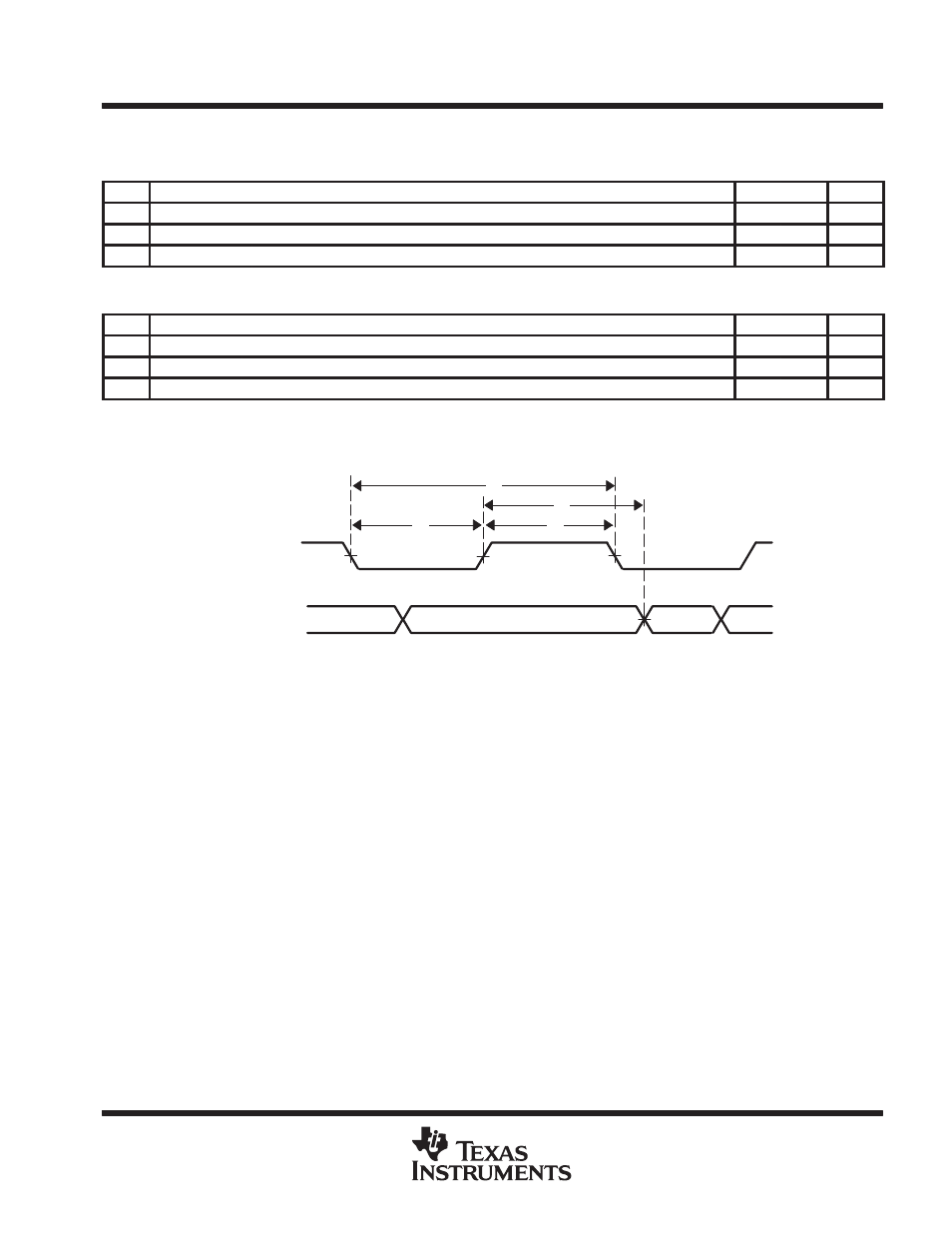

timing requirements (see Figure 15)

NO.

MIN

MAX

UNIT

1

tc(MxxTCLK)

Cycle time, MxxTCLK

25

25

ns

2

tw(MxxTCLKL)

Pulse duration, MxxTCLK low

ns

3

tw(MxxTCLKH)

Pulse duration, MxxTCLK high

14

ns

operating characteristics over recommended operating conditions (see Note 8 and Figure 15)

NO.

PARAMETER

MIN

MAX

UNIT

4†

td(MxxTXD)

Delay time, from MxxTCLK

↑

to MxxTXD3–MxxTXD0 valid

0

25

ns

4†

td(MxxTXEN)

Delay time, from MxxTCLK

↑

to MxxTXEN valid

0

25

ns

4†

td(MxxTXER)

Delay time, from MxxTCLK

↑

to MxxTXER valid

0

25

ns

† xx = ports 24, 25, and 26

NOTE 8: Both MxxCRS and MxxCOL are driven asynchronously by the PHY. MxxTXD3–MxxTXD0 is driven by the reconciliation sublayer

synchronous to the MxxTCLK. MxxTXEN is asserted and deasserted by the reconciliation sublayer synchronous to the MxxTCLK rising

edge. MxxTXER is driven synchronous to the rising edge of MxxTCLK.

ООО

ООО

ООООООООООО

ООООООООООО

4

MxxTXD3–MxxTXD0

MxxTXEN

MxxTXER

(outputs)

MxxTCLK

(input)

2

3

1

Figure 15. 10-/100-Mbit/s Transmit Ports