Texas Instruments THUNDER TNETX3270 User Manual

Page 52

TNETX3270

ThunderSWITCH

24/3 ETHERNET

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

52

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

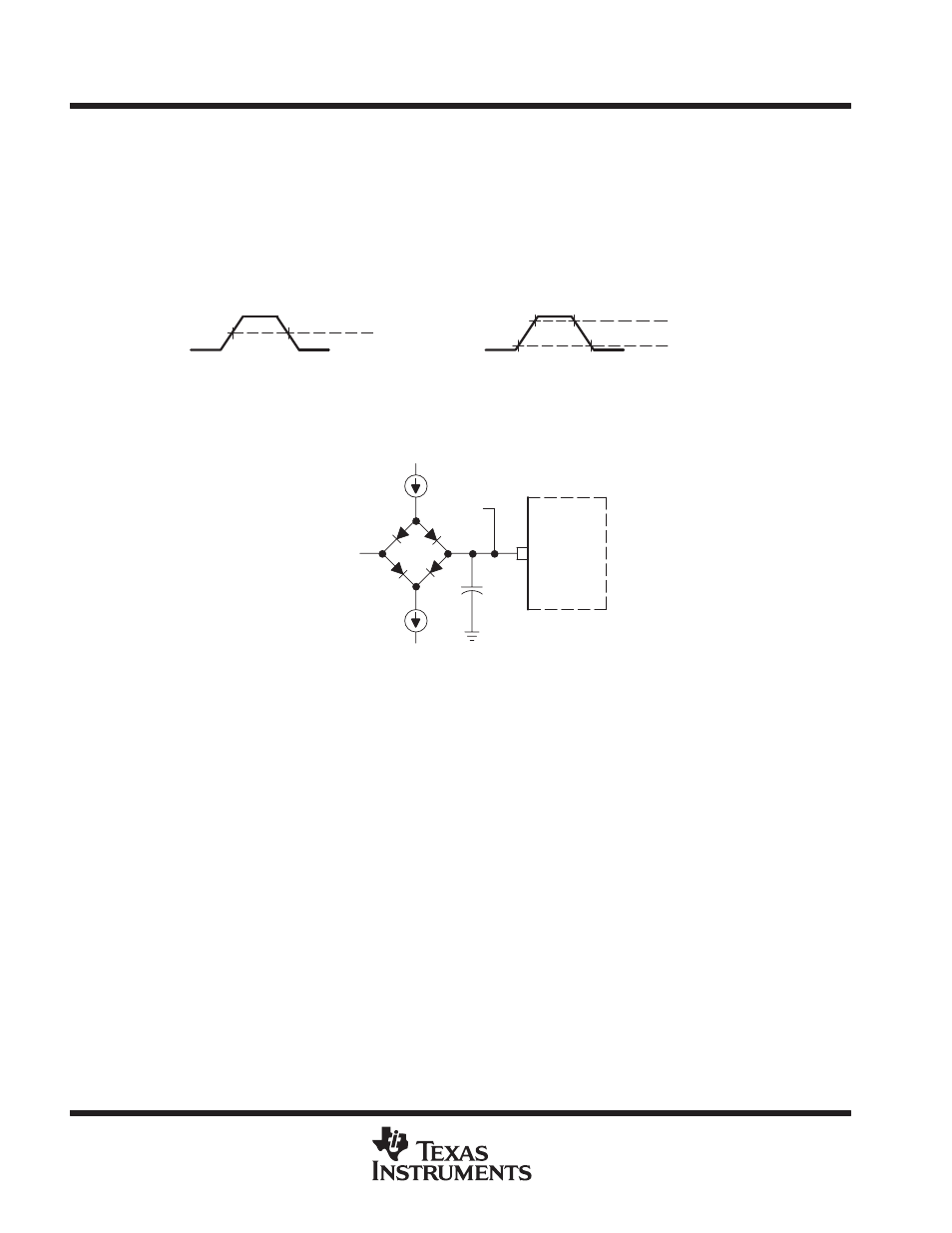

Outputs are driven to a minimum high-logic level of 3.3 V and to a maximum low-logic level of 0 V.

Output transition times are specified as follows: For a high-to-low transition on either an input or output signal, the

level at which the signal is said to be no longer high is 1.4 V and the level at which the signal is said to be low is 1.4 V.

For a low-to-high transition, the level at which the signal is said to be no longer low is 0.8 V and the level at which

the signal is said to be high is 2 V, as shown in the following.

The rise and fall times are not specified but are assumed to be those of standard TTL devices, which are typically

1.5 ns.

0.8 V (low)

2 V (high)

1.4 V

test measurement

The test-and-load circuit shown in Figure 12 represents the programmable load of the tester pin that is used

to verify timing parameters of the TNETX3270 output signals.

TTL OUTPUT TEST LOAD

CL

IOH

VLOAD

IOL

Where: I

OL

= Refer to I

OL

in recommended operating conditions.

I

OH

= Refer to I

OH

in recommended operating conditions.

V

LOAD

= 1.5 V, typical dc-level verification or

1.5 V, typical timing verification

C

L

= 45 pF, typical load-circuit capacitance

TTL

Output

Under

Test

Test

Point

Figure 12. Test-and-Load Circuit