Texas Instruments THUNDER TNETX3270 User Manual

Page 31

TNETX3270

ThunderSWITCH

24/3 ETHERNET

SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B – NOVEMBER 1997 – REVISED APRIL 1999

31

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

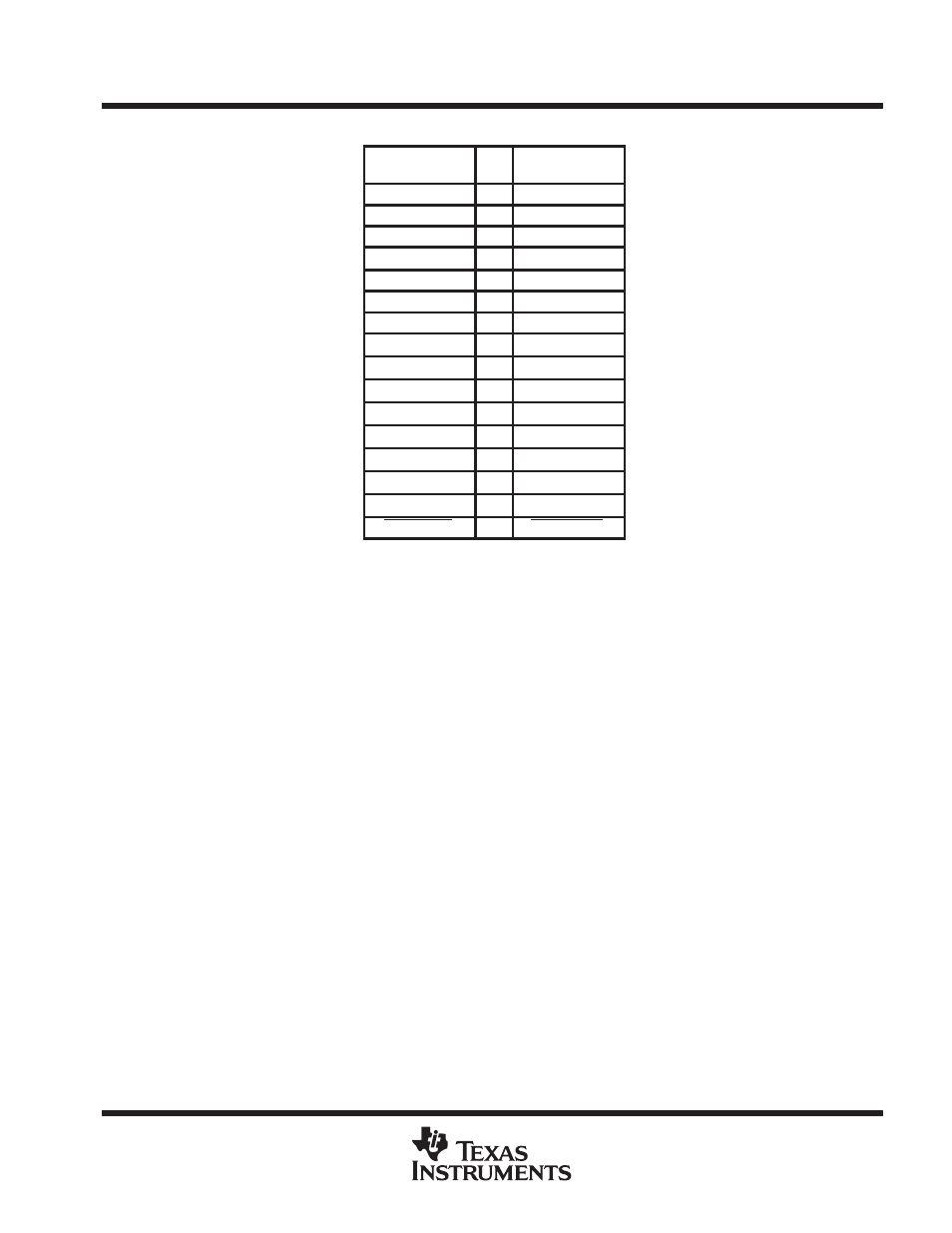

Table 11. 10-Mbit/s Interface Connections

TNETX3270

TERMINAL

TNETE2008

TERMINAL

THxCLK

←

IFCLK

THxSYNC

←

IFSYNC

THxCOL

←

IFCOL

THxCRS

←

IFCRS

THxLINK

←

IFLINK

THxRXD3

←

IFRXD3

THxRXD2

←

IFRXD2

THxRXD1

←

IFRXD1

THxRXD0

←

IFRXD0

THxRXDV

←

IFRXDV

THxTXD3

→

IFTXD3

THxTXD2

→

IFTXD2

THxTXD1

→

IFTXD1

THxTXD0

→

IFTXD0

THxTXEN

→

IFTXEN

THxRENEG

→

IFFORCEHD

Where x = 0, 1, or 2

The time multiplexing of this interface is shown in Figure 6. The interface runs synchronous to the

PHY-generated 20-MHz clock IFCLK. The MAC-to-PHY information for the first port in each group of eight (i.e.,

port 00, port 08, or port 16) is presented on the interface when the THxSYNC terminal is high. The next clock

cycle that the interface carries is the information for the second port. This process continues for all eight ports,

each using the interface for one cycle. When all ports have been processed in this manner, the sequence

resumes with the first port and again when the THxSYNC signal is asserted.

To improve latency-related issues, the PHY-to-MAC data are skewed by two slots, allowing the MAC to respond

to the input signals from the PHY in the same 400-ns cycle, rather than waiting for the next 400-ns cycle (which

would be the case if the signals were not skewed).