3 dm642 virtual i2c register details, Register – Texas Instruments TVP5154EVM User Manual

Page 28

www.ti.com

9.2.3

DM642 Virtual I

2

C Register Details

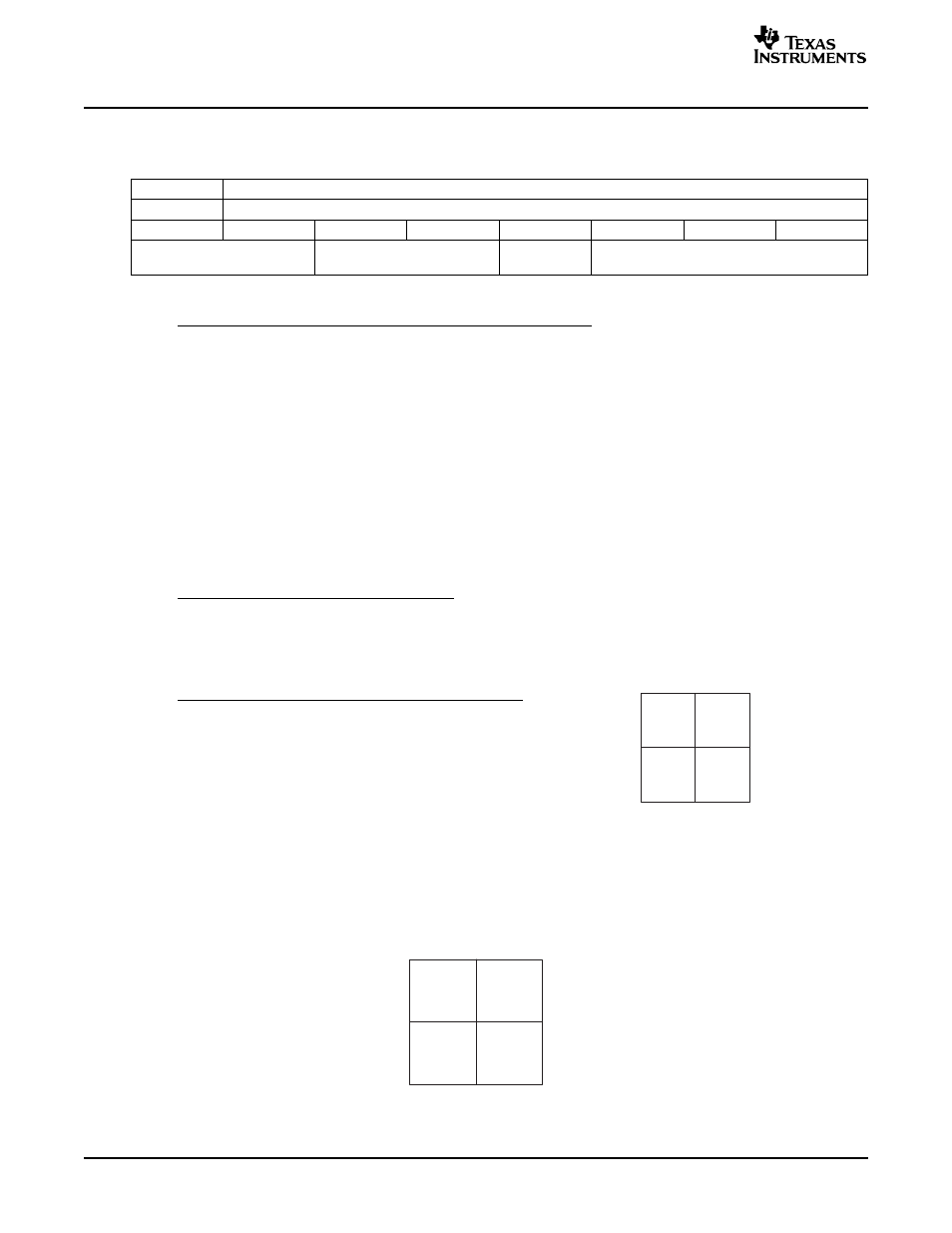

Quad 1

Quad 2

Quad 3

Quad 4

Decoder 1

Scaled

Decoder 2

Unscaled

Decoder 2

Unscaled

Decoder 4

Scaled

Programming the TMS320DM642

Table 10. Decoder 1 Register

Address

00h

Default

02h

7

6

5

4

3

2

1

0

Capture

Reserved

Position

Capture Size

Enable

Capture Size

Bit 2

Bit 1

Bit 0

Unscaled

0

0

0

QSIF – 176

×

120

0

0

1

SIF – 352

×

240 (1/4 NTSC)

0

1

0

(default)

QCIF – 176

×

144

0

1

1

CIF – 352

×

288 (1/4 PAL)

1

0

0

QVGA – 320

×

240

1

0

1

VGA – 640

×

480

1

1

0

Reserved

1

1

1

Capture Enable

Bit 3

Disable (default)

0

Enable

1

Position

Bit 5

Bit 4

Quadrant 1 (default)

0

0

Quadrant 2

0

1

Quadrant 3

1

0

Quadrant 4

1

1

Scaled capture sizes always take priority over unscaled capture sizes.

Decoder priorities are always such that Decoder 1 is the highest priority, Decoder 2 is the second highest,

etc.

For example, if Decoders 1 and 4 are scaled to 1/4 size and Decoders 2 and 3 are unscaled, this display

results:

28

TVP5154EVM User's Guide

SLEU069A – February 2006 – Revised July 2006