3 external sdram, Functional overview – Renesas M3A-HS60 User Manual

Page 20

Functional Overview

2.3.3 External SDRAM

Rev.1.00 June 1,2005

2-6

REJ11J0002-0100Z

2

2.3.3 External SDRAM

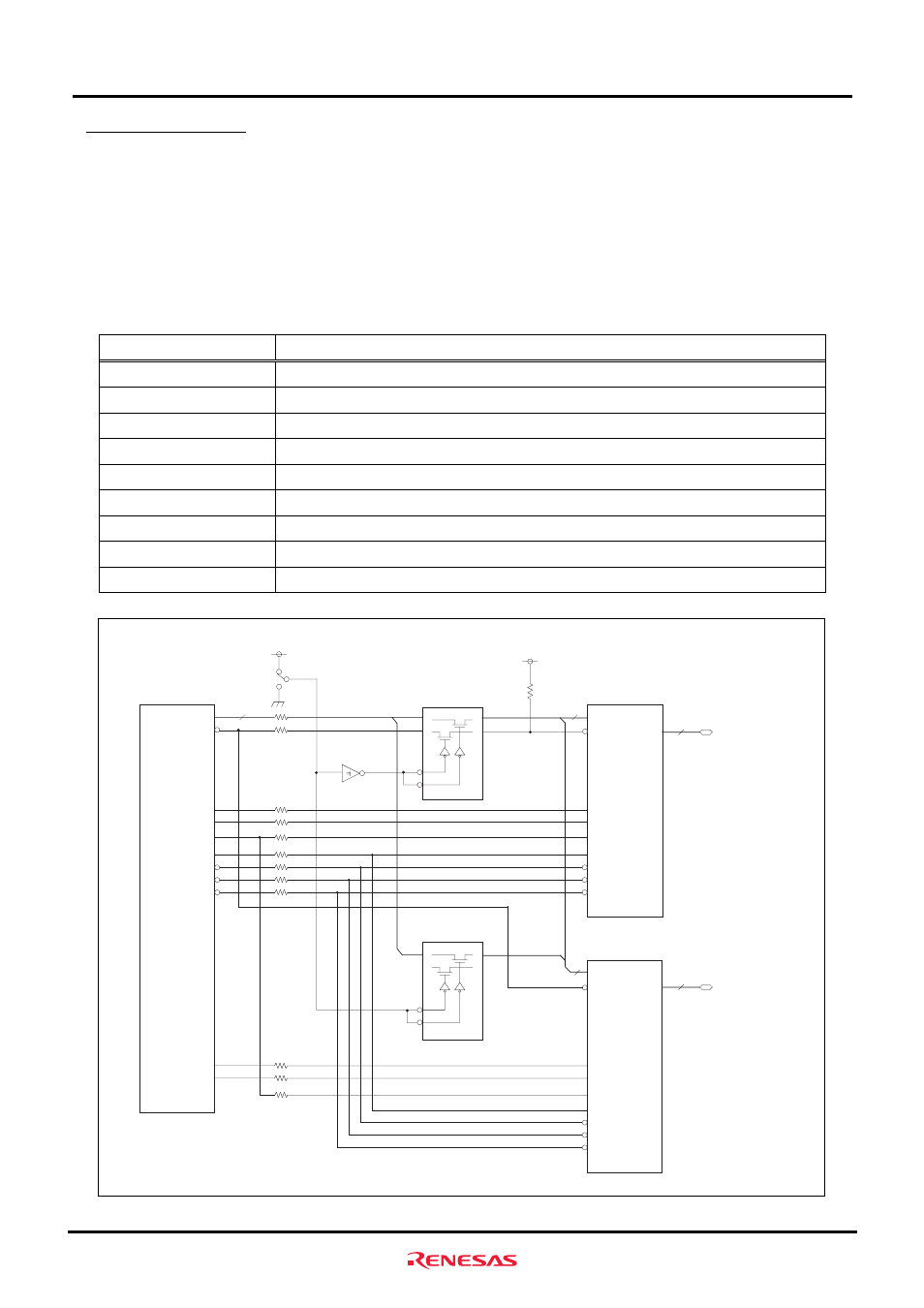

The M3A-HS60 includes two pcs. of 16-Mbyte SDRAM (for an external SDRAM) as standard equipment.

The SH7206's internal bus state controller can be used to control the SDRAM.

Note that the SDRAM can be switched between 32-bit bus access and 16-bit bus access. (For 16-bit bus access, only

one pc. of 16-Mbyte SDRAM can be used.)

Table2.3.3 lists SDRAM specifications used in M3A-HS60. Figure2.3.3 shows a block diagram of SDRAM.

Table2.3.3 SDRAM Specifications Used in M3A-HS60

Specification Content

Part number

EDS1216AATA-75E

Configuration

16 Mbytes (16-bit bus width) x 2pcs.

Capacity 32

Mbytes

Access time

5.4ns

CAS latency

2 (At 66MHz bus clock)

Refresh interval

4,096 refresh cycles every 64ms

Row address

A11- A0

Column address

A8 - A0

Number of banks

4-bank operation controlled by BA0 and BA1

A15-1

SH7206

14

CKE

CS3#

RASL#

DQMUU

DQMUL

CKIO

CASL#

RD/WR#

DQMLU

DQMLL

MA11-0,BA1-0

EDS1216AATA

(8Mx16 bits)

RAS#

CKE

CS#

DQML

DQMU

CLK

CAS#

WE#

DQ15-DQ0

1OE#

2OE#

A[12:1], A14-13

32-bit Access

MA11-0,BA1-0

EDS1216AATA

(8Mx16 bits)

RAS#

CKE

CS#

DQML

DQMU

CLK

CAS#

WE#

DQ15-DQ0

3.3V

14

14

16

SH72060 D31-D16

16

SH72060 D15-D0

1OE#

2OE#

A[13:2], A15-14

16-bit Access

3.3V

SDRAM

bus size setting

SDRAM_SZ

SDRAM_SZ=Low:16-bit access using SDRAMx1

SDRAM_SZ=High:32-bit access using SDRAMx2

Figure2.3.3 Block Diagram of External SDRAM