Figure 3-25. trailing edge output timing diagram – National Instruments 653X User Manual

Page 79

Chapter 3

Timing Diagrams

3-28

ni.com

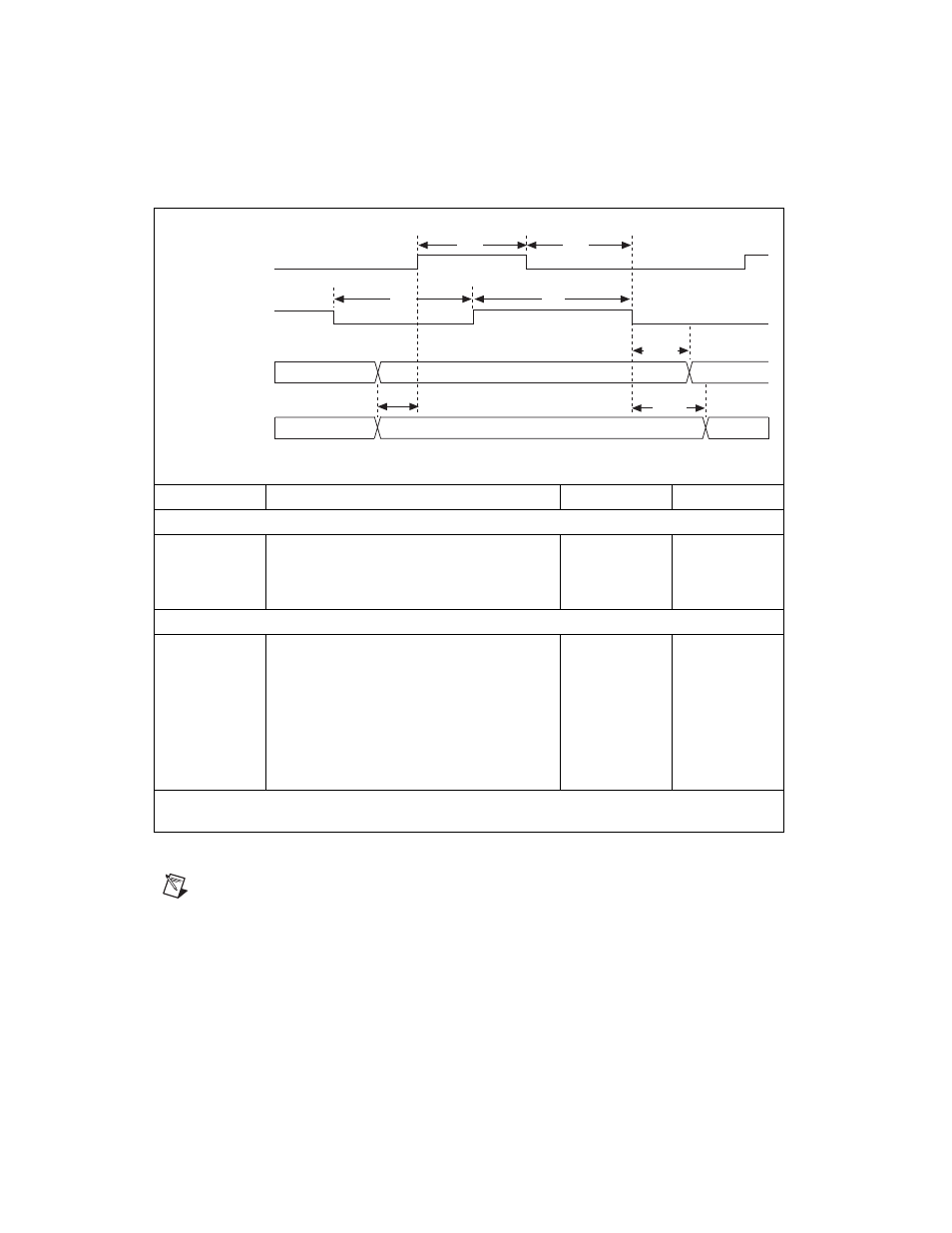

Figure 3-25. Trailing Edge Output Timing Diagram

Note

When REQ-edge latching is disabled (default), output data valid will be held

t

r*do(1)

ns after the trailing edge of REQ occurs. With REQ-edge latching enabled, output

data will be held at most t

r*do(1)

ns after the trailing edge of REQ occurs.

Parameter

Description

Minimum

Maximum

Input Parameters

t

rr*

REQ pulse width

75

—

t

r*r

REQ inactive duration

75

—

t

a*r*

ACK inactive to next REQ inactive

0

—

Output Parameters

t

aa*

ACK pulse width

225

1

275

2

t

r*do(1)

REQ inactive to new output data

(with REQ-edge latching)

0

50

t

r*do(2)

REQ inactive to new output data

(with REQ-edge latching disabled)

0

—

t

doa

Output data valid to ACK

(with REQ-edge latching disabled)

25

—

1

t

aa*

(min)

= 225 + programmable delay

2

t

aa*

(max) = 275 + programmable delay

REQ

Output Data Valid

(REQ-edge

latching)

Output Data Valid

(REQ-edge

latching disabled)

t

r*r

t

r*do(1)

t

doa

t

aa*

t

a*r*

t

rr*

ACK

t

r*do(2)

ACK and REQ are shown as active high