Figure 3-5. burst input timing diagram (default) – National Instruments 653X User Manual

Page 59

Chapter 3

Timing Diagrams

3-8

ni.com

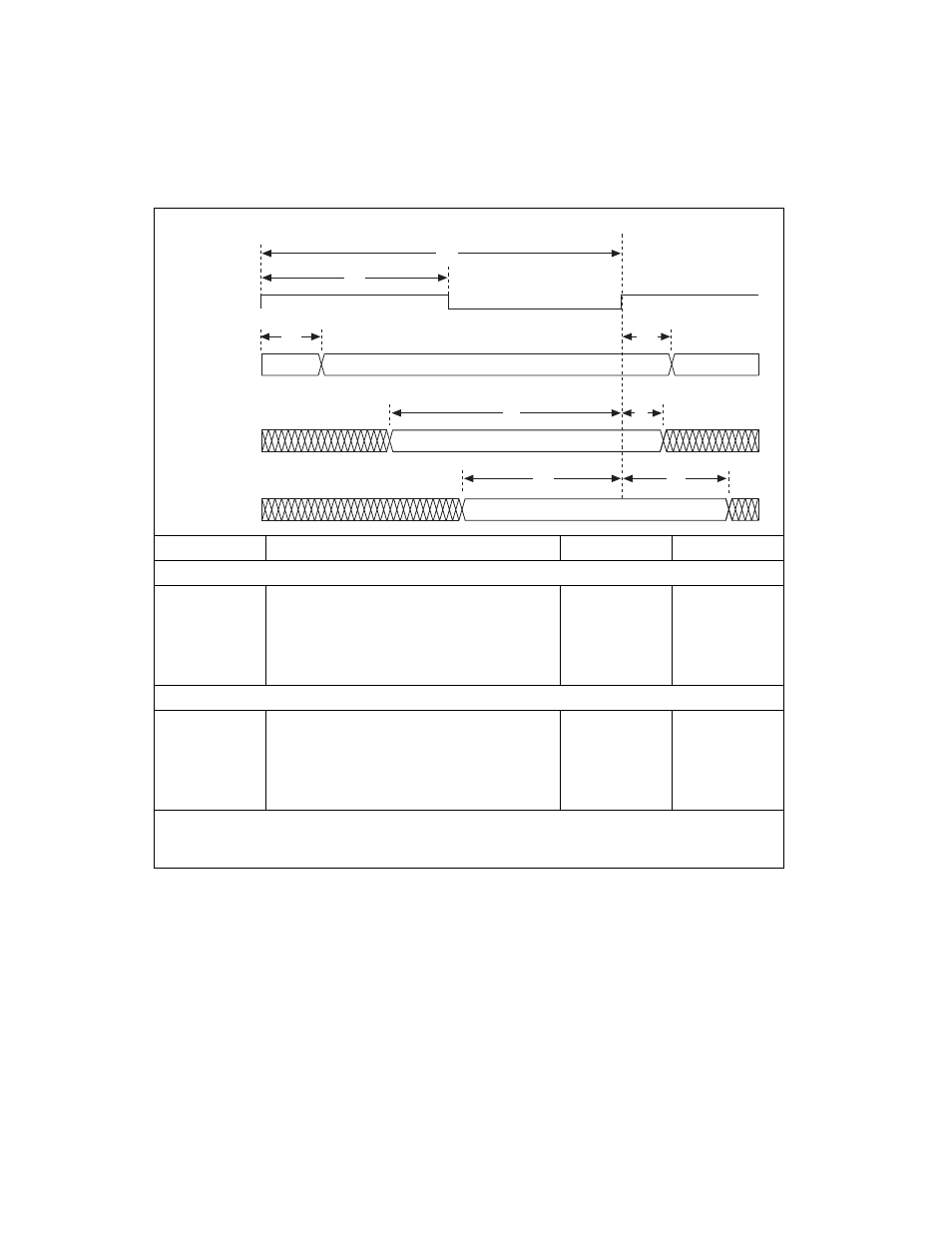

Figure 3-5. Burst Input Timing Diagram (Default)

Parameter

Description

Minimum

Maximum

Input Parameters

t

rs

Setup time from REQ valid to PCLK

12

—

t

rh

Hold time from PCLK to REQ invalid

0

—

t

dis

Setup time from input data valid to PCLK

4

—

t

dih

Hold time from PCLK to input data invalid

6

—

Output Parameters

t

pc

PCLK cycle time

50

700

1

t

pw

PCLK high pulse duration

t

pc

/2 – 5

t

pc

/2 + 5

t

pa

PCLK to ACK valid

—

18

t

ah

Hold time from PCLK to ACK invalid

3

—

1

t

pc

= programmable delay from 100 to 700 ns, or 50 ns if programmable delay is 0. Timebase stability for the onboard

20 MHz clock source is 100 ppm.

All timing values are in nanoseconds.

PCLK

ACK

Data In Valid

REQ

t

dis

t

dih

t

rs

t

pa

t

pw

t

pc

t

rh

t

ah

See also other documents in the category National Instruments Computer Accessories:

- R Series Intelligent DAQ PXI-784xR (14 pages)

- 7344 (66 pages)

- Relay Module SCC-RLY01 (9 pages)

- Compact FieldPoint Mounting Accessories cFP-21xx (10 pages)

- PCI-4451 (115 pages)

- NI 6239 (172 pages)

- SCXI-1190 (54 pages)

- SCXI-1190/1191 (45 pages)

- NI 785xR (74 pages)

- DIO 6533 (125 pages)

- Multisystem eXtension Interface NI PCIe-836x (37 pages)

- GPIB-BUF (40 pages)

- 6527 (47 pages)

- PCI-8336 (43 pages)

- PXI NI PXI-8105 (73 pages)

- 6025E (136 pages)

- NI 78xxR (12 pages)

- PCI-6110E/6111E (113 pages)

- NI 6115/6120 (127 pages)

- 1128 (97 pages)

- 800 Series (104 pages)

- NI 6115 (127 pages)

- NI 784xR (74 pages)

- GPIB-100A (43 pages)

- VXI-MIO Series (151 pages)

- Low-Cost Multifunction I/O Board for ISA Lab-PC+ (211 pages)

- PC-DIO-24/PnP (107 pages)

- PC-LPM-16/PnP (125 pages)

- NI 7831R (71 pages)

- VXI/VME 600 (61 pages)

- PXI NI PXI-1052 (70 pages)

- PC-DIO-96 (105 pages)

- NI UES-3880 (14 pages)

- GPIB-COM (56 pages)

- Switch Executive (8 pages)

- AT-MIO-16X (330 pages)

- 7340 PCI (67 pages)

- NI 783xR (73 pages)

- NI CVS-1450 Series (91 pages)

- SCXI-1321 (16 pages)