Deciding the width of data to transfer, Table 2-3. port and timing controller combinations, Deciding the width of data to transfer -17 – National Instruments 653X User Manual

Page 35: Generating and receiving digital patterns and, Waveforms—pattern i/o, Section

Chapter 2

Using Your 653X

© National Instruments Corporation

2-17

The preloading process will cause a small delay between the start command

in software and the actual start of data transfer. If this is a concern, you may

disable the preloading by calling the following function/VI before the

software start command:

•

NI-DAQ C interface—In the

Set_DAQ_Device_Info

function, set

the ND_FIFO_Transfer_COUNT to ND_NONE.

•

LabVIEW—In the DIO Parameter VI, set the Scarabs Preload Enable

attribute to OFF.

Generating and Receiving Digital Patterns and

Waveforms—Pattern I/O

Using pattern I/O, you can acquire or generate patterns on every rising or

falling edge of a clock signal. The clock signal can be generated internally

by an onboard 32-bit counter set to a user-specified frequency or the clock

signal can be received from the REQ pin in the I/O connector.

Note

Feed external clocking signals into the PCLK pin for burst-mode handshaking and

into the REQ pin when performing pattern I/O.

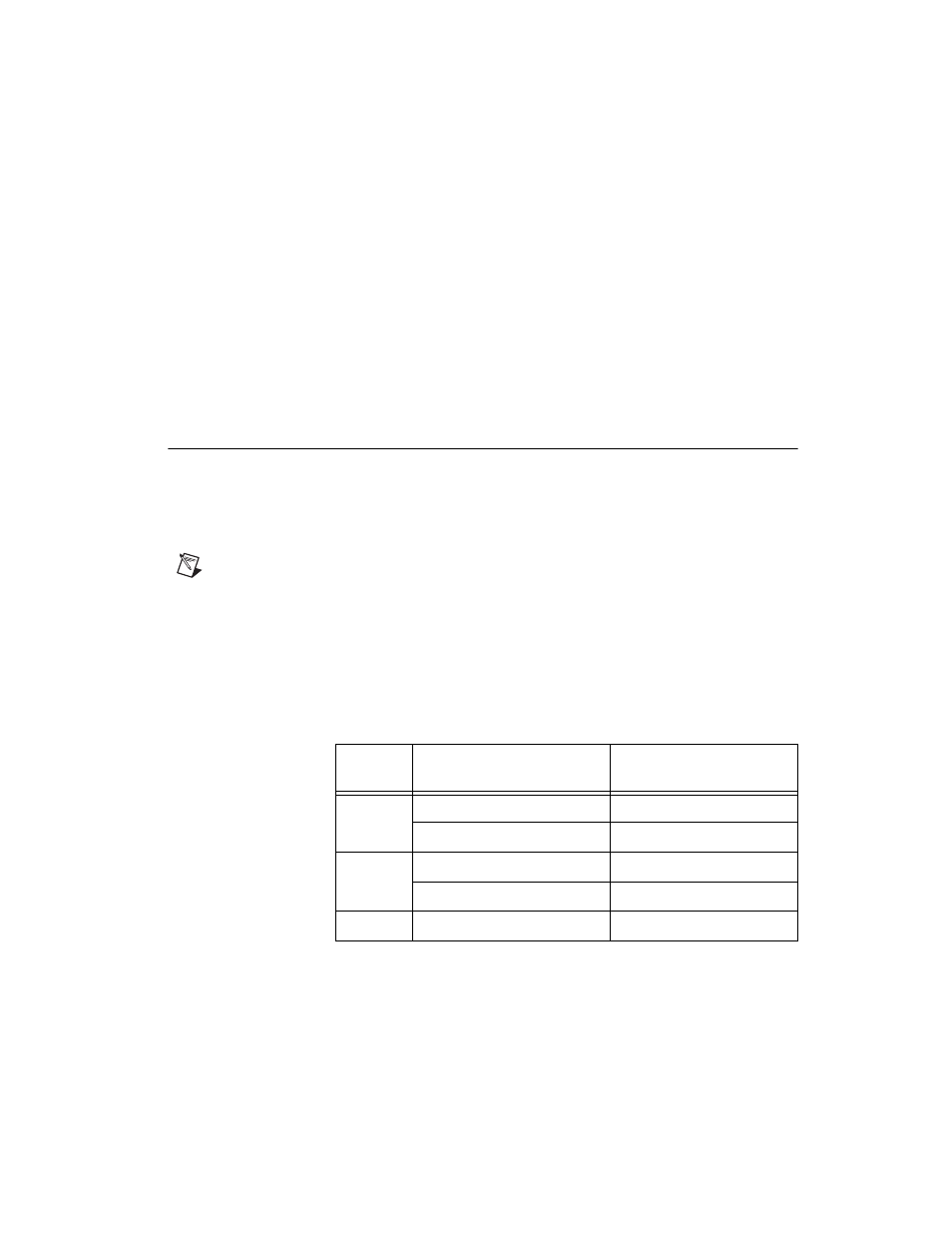

Deciding the Width of Data to Transfer

You can choose between a width of eight, 16, or 32 bits. Use the following

table to find the valid combinations of ports and timing controllers you can

use based on the width of data you want to transfer.

Table 2-3. Port and Timing Controller Combinations

Transfer

Width

Possible Port

Combinations

Timing Controllers

That Can Be Used

8 bits

Port 0 (DIOA<0..7>)

Group 1

Port 2 (DIOC<0..7>)

Group 2

16 bits

Port 0, Port 1

Group 1

Port 2, Port 3

Group 2

32 bits

Port 0, Port 1, Port 2, Port 3

Group 1