Paradise P300 User Manual

Page 177

P300H

P300 Series Modem Installation and Operating Handbook

Page 177

Eurocom D/1 interface `D` operation

The Eurocom `D` interface uses transformer coupled differential clock and data signals. The data signal

is AMI coded, and the amplitude of both clock and data signals is ±0.5V (ie 1.0 V peak to peak). The

differential lines are of 130

S

impedance, and the centre tap of the line coupling transformers may either

be grounded, or left floating.

The Eurocom `D` interface will operate from <16kbps to >2048kbps, although the Eurocom specification

call for only 256, 512, and 1024kbps. In addition to the clock and data lines in and out (four lines), a fifth

line is implemented over and above the Eurocom specification which carries the modems internal clock out

when the Tx clock is set to internal.

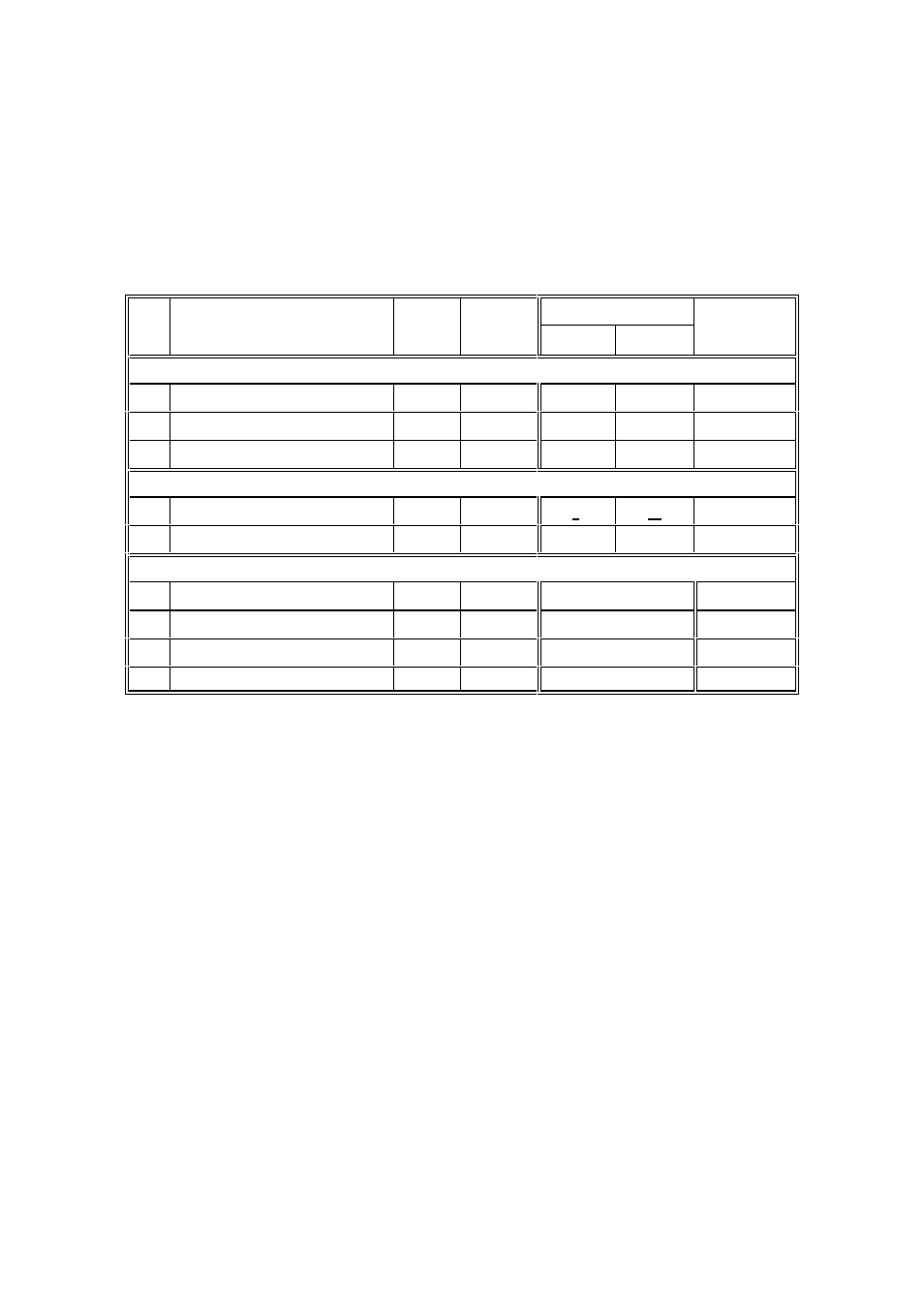

Min

RS422

Circuit

Req

Name

Number

Signal Description

centre tap of

25 pin

Link to ground

transformer

A

B

DATA CIRCUIT TOWARDS MODEM (TX)

U

Clock In

TT

113

19

6

LK 1 *

U

Data In

SD

103

18

5

LK 2 *

Int’ Tx Clock Out

ST

114

21

8

LK 7 *

DATA CIRCUIT FROM MODEM (RX)

U

Clock Out

RT

115

4

17

LK 4 *

U

Data Out

RD

104

16

3

LK 5 *

COMMON LINES

U

Ground to Activate Eurocom `D` 14

n/a

Do Not Connect

12, 20

n/a

U

Signal Ground

SG

102

2, 7, 13, 15, 22, 25

n/a

U

Shield/Protective ground

PG

101

1

n/a

* Links

All links settings are:

Centre tap grounded: 1-2 (link `up` with the PCB legend the right way up)

Centre tap floating 2-3 (link `down` with the PCB legend the right way up)

The typical configuration would normally be to ground the outputs, and leave the inputs floating ie:

Links 4, 5, and 7 in pos 1-2 (up), and links 1 and 2 in pos 2-3 (down)

This provides protection by ensuring the signal levels remain close to ground potential (as might happen

if both inputs and outputs were floating), but avoid any ground currents between distant locations (as might

happen if both inputs and outputs were grounded).

The modem will detect and display the `Data Marginal` warning if the Tx input clock and data phase is

incorrect, and will automatically flip the clock phase to correct this. If repeated `Data Marginal` alarms occur

then it is likely the Tx clock and data are not from the same clock course and are `slipping past` each other.