Chapter 10 appendices, Instruction set – Panasonic MN101C00 User Manual

Page 156

Chapter 10 Appendices

142

Instruction Set

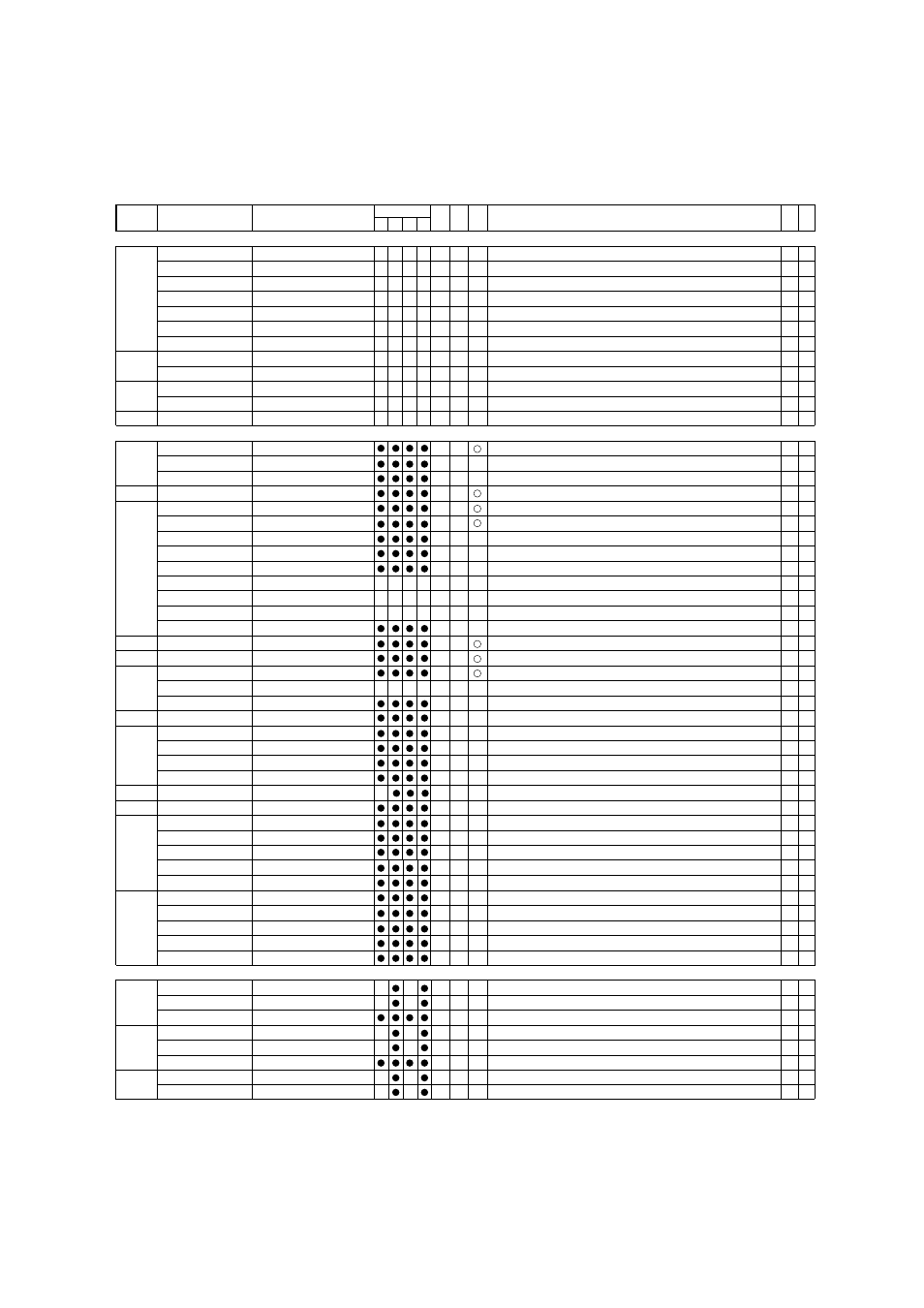

MN101C00 SERIES INSTRUCTION SET

Group

Mnemonic

Operation

Affected Flag

VF NF CF ZF

Code

Size

Cycle Re-

peat

Machine Code

Notes Page

1

2

3

4

5

6

7

8

9

10

11

Expand

PUSH Dn

PUSH

SP-1

→

SP,Dn

→

mem8(SP)

–

–

–

–

2

3

1111 10Dn

PUSH An

SP-2

→

SP,An

→

mem16(SP)

–

–

–

–

2

5

0001 011A

POP Dn

POP

mem8(SP)

→

Dn,SP+1

→

SP

–

–

–

–

2

3

1110 10Dn

POP An

mem16(SP)

→

An,SP+2

→

SP

–

–

–

–

2

4

0000 011A

EXT Dn,DWm

EXT

sign(Dn)

→

DWm

–

–

–

–

3

3

1001 000d

0010

Arithmetic instructions

ADD Dn,Dm

ADD

Dm+Dn

→

Dm

3

2

0011 DnDm

0011

ADD imm4,Dm

Dm+sign(imm4)

→

Dm

3

2

1000 00Dm <#4>

ADD imm8,Dm

Dm+imm8

→

Dm

4

2

0000 10Dm <#8.

...>

ADDC Dn,Dm

ADDC

Dm+Dn+CF

→

Dm

3

2

1011 DnDm

0011

ADDW DWn,DWm

ADDW

DWm+DWn

→

DWm

3

3

0101 00Dd

0010

ADDW DWn,Am

Am+DWn

→

Am

3

3

0101 10Da

0010

ADDW imm4,Am

Am+sign(imm4)

→

Am

3

2

1110 110a <#4>

ADDW imm8,Am

Am+sign(imm8)

→

Am

5

3

1110 110a <#8.

...>

0010

ADDW imm16,Am

Am+imm16

→

Am

7

4

0101 011a <#16

....

....

...>

0010

ADDW imm4,SP

SP+sign(imm4)

→

SP

–

–

–

–

3

2

1111 1101 <#4>

ADDW imm8,SP

SP+sign(imm8)

→

SP

–

–

–

–

4

2

1111 1100 <#8.

...>

ADDW imm16,SP

SP+imm16

→

SP

–

–

–

–

7

4

1111 1100 <#16

....

....

...>

0010

ADDW imm16,DWm

DWm+imm16

→

DWm

7

4

0101 010d <#16

....

....

...>

0010

ADDUW Dn,Am

ADDUW

Am+zero(Dn)

→

Am

3

3

1000 1aDn

0010

ADDSW Dn,Am

ADDSW

Am+sign(Dn)

→

Am

3

3

1001 1aDn

0010

SUB Dn,Dm(when Dn

≠

Dm)

SUB

Dm-Dn

→

Dm

3

2

1010 DnDm

0010

SUB Dn,Dn

Dn-Dn

→

Dn

0

0

0

1

2

1

1000 01Dn

SUB imm8,Dm

Dm-imm8

→

Dm

5

3

1010 DmDm <#8.

0010

SUBC Dn,Dm

SUBC

Dm-Dn-CF

→

Dm

3

2

1011 DnDm

0010

SUBW DWn,DWm

SUBW

DWm-DWn

→

DWm

3

3

0100 00Dd

0010

SUBW DWn,Am

Am-DWn

→

Am

3

3

0100 10Da

0010

SUBW imm16,DWm

DWm-imm16

→

DWm

7

4

0100 010d <#16

....

....

...>

0010

SUBW imm16,Am

Am-imm16

→

Am

7

4

0100 011a <#16

....

....

...>

0010

MULU Dn,Dm

MULU

Dm

∗

Dn

→

DWk

0

3

8

1111 111D

0010

DIVU Dn,DWm

DIVU

DWm/Dn

→

DWm-I...DWm-h

3

9

1110 111d

0010

MOVW imm16,Am

imm16

→

Am

–

–

–

–

6

3

54

55

55

56

56

57

57

58

58

59

59

60

61

61

62

63

64

64

65

65

66

66

67

67

68

69

70

71

71

72

73

74

74

75

75

76

77

1101 111a <#16

....

....

...>

MOVW SP,Am

SP

→

Am

–

–

–

–

3

3

0000 100a

0010

MOVW An,SP

An

→

SP

–

–

–

–

3

3

0000 101A

0010

MOVW DWn,DWm

DWn

→

DWm

–

–

–

–

3

3

1000 00Dd

0010

MOVW DWn,Am

DWn

→

Am

–

–

–

–

3

3

0100 11Da

0010

MOVW An,DWm

An

→

DWm

–

–

–

–

3

3

1100 11Ad

0010

MOVW An,Am

An

→

Am

–

–

–

–

3

3

0000 00Aa

0010

∗

3

∗

6

∗

1

∗

6

∗

7

∗

6

∗

7

∗

8

∗

1

∗

4

∗

5

∗

1

∗

1

D=DWn, d=DWm

∗

2

A=An, a=Am

∗

3

d=DWm

∗

4

D=DWk

∗

5

D=DWm

∗

6

#4 sign extended

∗

7

#8 sign extended

∗

8

Dn zero extended

CMP Dn,Dm

CMP

Dm-Dn...PSW

3

2

0010 DnDm

0011

CMP imm8,Dm

Dm-imm8...PSW

4

2

1100 00Dm <#8.

...>

CMP imm8,(abs8)

mem8(abs8)-imm8...PSW

6

3

0000 0100

78

78

79

CMP imm8,(abs12)

mem8(abs12)-imm8...PSW

7

3

79

80

81

81

82

82

83

0000 0101 ...> <#8. ...> CMP imm8,(abs16) mem8(abs16)-imm8...PSW 9 5 1101 1000 .... ...> <#8. ...> 0011 CMPW DWn,DWm CMPW DWm-DWn...PSW 3 3 1000 01Dd 0010 CMPW DWn,Am Am-DWn...PSW 3 3 0101 11Da 0010 CMPW An,Am ∗ 1 ∗ 2 Am-An...PSW 3 3 0000 01Aa 0010 CMPW imm16,DWm DWm-imm16...PSW 6 3 1100 110d <#16 .... .... ...> CMPW imm16,Am Am-imm16...PSW 6 3 1101 110a <#16 .... .... ...> Logical instructions AND Dn,Dm AND Dm&Dn → Dm 0 0 3 2 0111 DnDm 0011 AND imm8,Dm Dm&imm8 → Dm 0 0 4 2 0001 11Dm <#8. ...> AND imm8,PSW PSW&imm8 → PSW 5 3 1001 0010 <#8. ...> 0010 OR Dn,Dm OR DmIDn → Dm 0 0 3 2 0110 DnDm 0011 OR imm8,Dm DmIimm8 → Dm 0 0 4 2 0001 10Dm <#8. ...> OR imm8,PSW PSWIimm8 → PSW 5 3 1001 0011 <#8. ...> 0010 XOR Dn,Dm XOR Dm^Dn → Dm 0 0 3 2 1010 DnDm 0011 XOR imm8,Dm Dm^imm8 → Dm 0 0 5 3 1010 DmDm <#8. ...> 0011 84 84 85 86 86 87 88 88 ...> <#8. ...> ∗ 2 ∗ 9 m ≠ n ∗ 9 Note: "Page" refers to the corresponding page in the Instruction Manual.