Pci connector j1 (front) – LSI U80ALVD User Manual

Page 61

Operational Environment

A-5

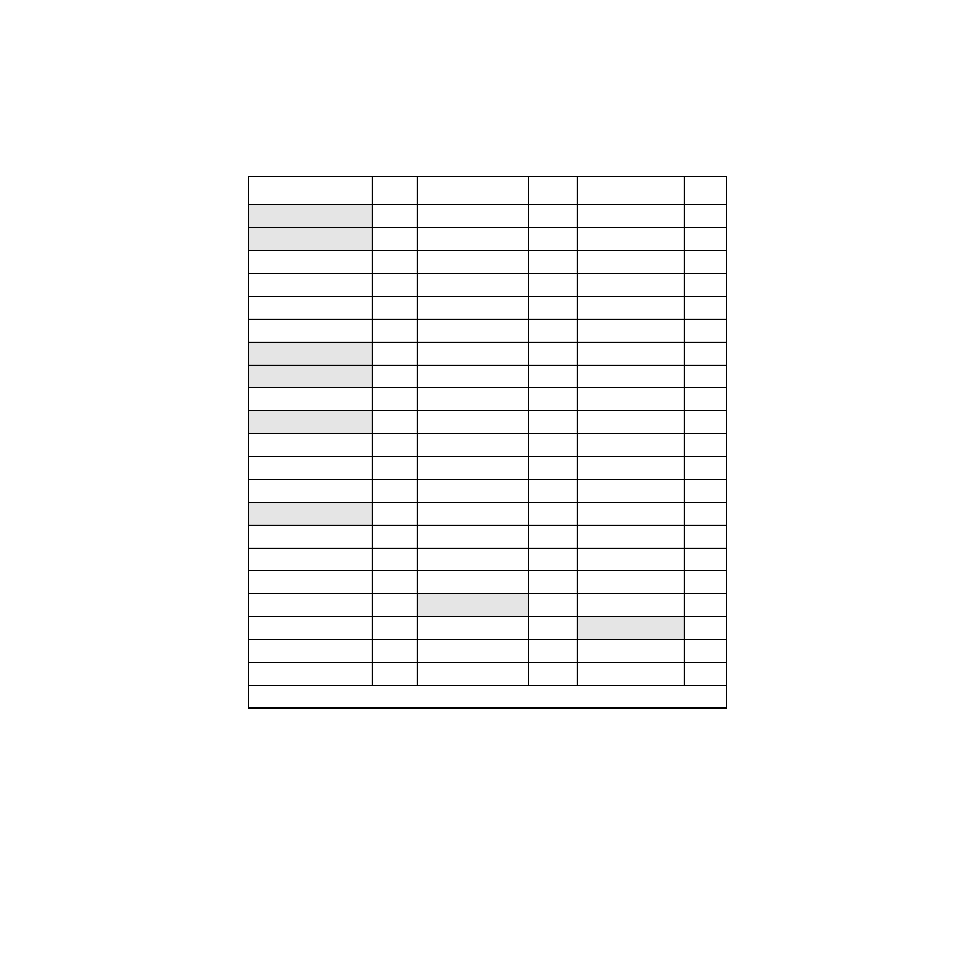

Table A.2

PCI Connector J1 (Front)

Signal Name

Pin

Signal Name

Pin

Signal Name

Pin

−

12 V

1

GND

22

SERR/

42

TCK

2

AD27

23

+3.3 V

43

GND

3

AD25

24

C_BE1/

44

TDO

4

+3.3 V

25

AD14

45

+5 V

5

C_BE3/

26

GND

46

+5 V

6

AD23

27

AD12

47

INTB/

7

GND

28

AD10

48

INTD/

8

AD21

29

GND

49

GND (PRSNT1/)

9

AD19

30

KEYWAY

50

RESERVED

10

+3.3 V

31

KEYWAY

51

GND (PRSNT2/)

11

AD17

32

AD08

52

KEYWAY

12

C_BE2/

33

AD07

53

KEYWAY

13

GND

34

+3.3 V

54

RESERVED

14

IRDY/

35

AD05

55

GND

15

+3.3 V

36

AD03

56

CLK

16

DEVSEL/

37

GND

57

GND

17

GND

38

AD01

58

REQ/

18

LOCK/

39

VI/O

59

VI/O

19

PERR/

40

ACK64/

60

AD31

20

+3.3 V

41

+5 V

61

AD29

21

+5 V

62

1. Highlighted signals are not connected.