4 advanced chipset setup – SMC Networks 486DX4 User Manual

Page 70

AR-B1462 User¡

¦s Guide

7-6

7.4 ADVANCED CHIPSET SETUP

This option controls the configuration of the board’ s chipset. Control keys for this screen are the same as for the

previous screen.

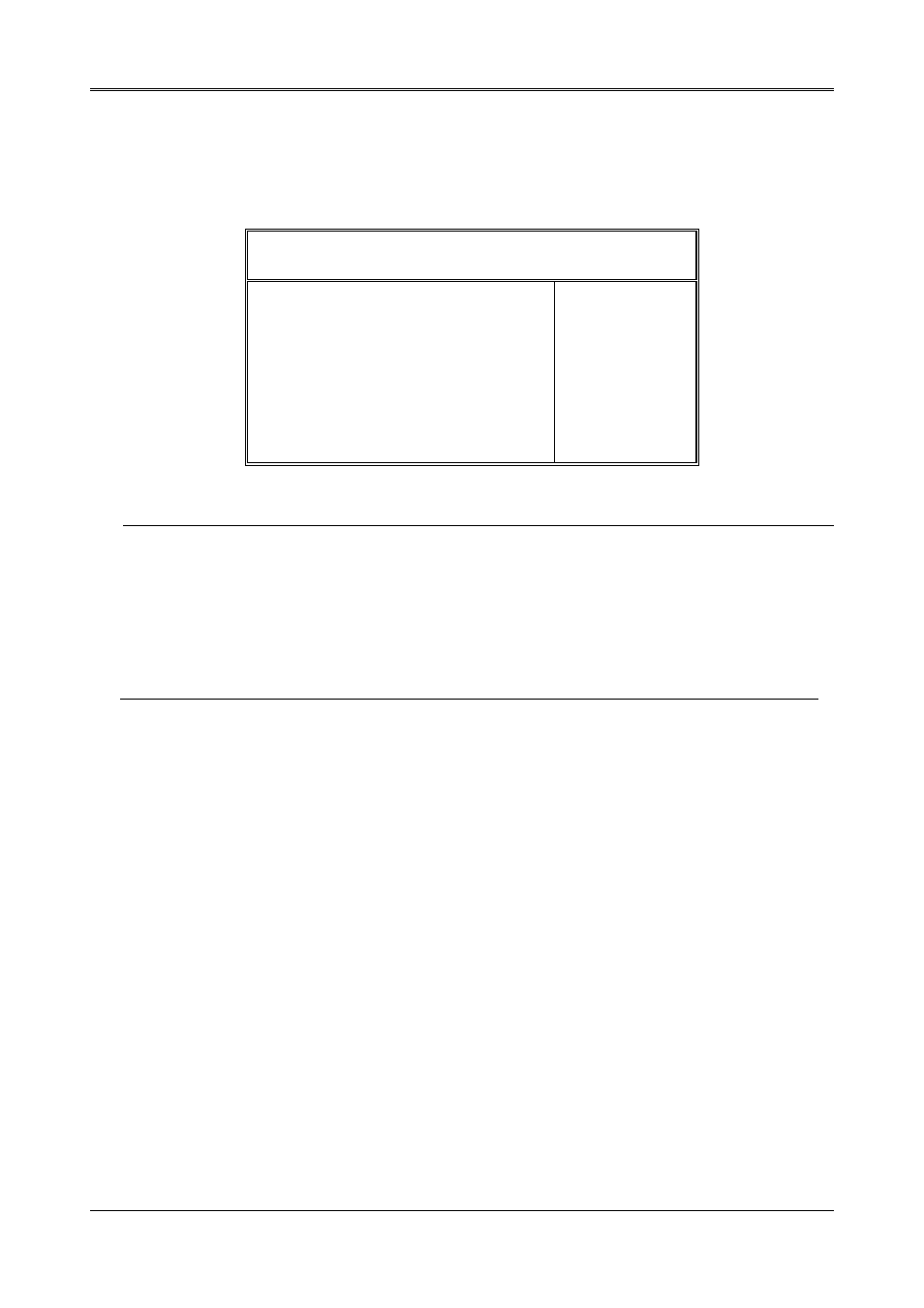

AMIBIOS SETUP - ADVANCED CHIPSET SETUP

(C) 1996 American Megatrends, Inc. All Rights Reserved

Auto Config Function

Enabled

AT Bus Clock

CLK/4

DRAM Read Timing

Normal

DRAM Write Timing

Normal

Memory Parity Check

Disabled

DRAM Hidden Refresh

Enabled

DRAM Refresh Period Setting

60us

Memory Hole At 15-16M

Disabled

ISA I/O Recovery

Disabled

ISA I/O Recovery time

1.5us

Available Options :

Disabled

Enabled

ESC:Exit ¡ ф

¡ х

:Sel

PgUp/PgDn:Modify

F2/F3:Color

Figure 7-4 BIOS: Advanced Chipset Setup

Automatic Configuration

If selecting a certain setting for one BIOS Setup option determines the settings for one or more other BIOS Setup

options, the BIOS automatically assigns the dependent settings and does not permit the end user to modify these

settings unless the setting for the parent option is changed. Invalid options are grayed and cannot be selected.

AT Bus Clock

This option sets the polling clock speed of ISA Bus (PC/104).

NOTE: 1. PCLK means the CPU inputs clock.

2. Acrosser recommends user setting at the range of 8MHz to 10MHz.

Memory Parity Check

This option Enables or Disables parity is error checking for all system RAM. This option must be Disabled if the

used DRAM SIMMs are 32-bit but not 36-bit devices.

Memory Hole at 15-16 M

This option specifies the range 15MB to 16MB in memory that cannot be addressed on the ISA bus.

ISA I/O Recovery

ISA I/O Recovery Time

These options specify the length of the delay (in BUSCLK) inserted between consecutive 8-bit/16-bit I/O

operations.