8 lvds (x7spa-l only), Bpp connector, Bpp lvds panel – SUPER MICRO Computer SUPER X7SPE-HF-D525 User Manual

Page 38: X7spa and x7spe motherboard series user's manual

1-26

X7SPA and X7SPE Motherboard Series User's Manual

1-8 LVDS (X7SPA-L only)

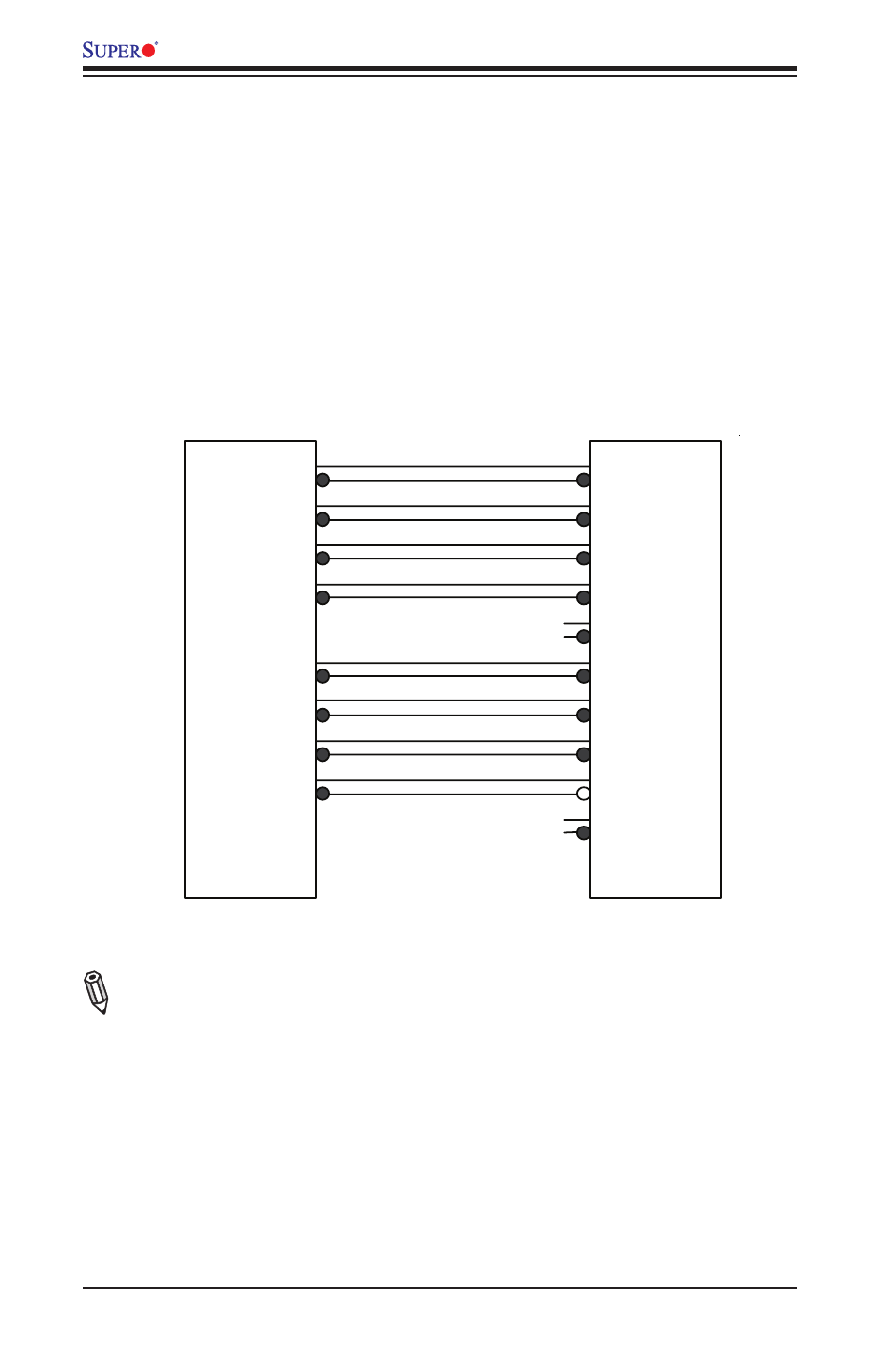

Low-Voltage Differential Signaling (LVDS) is an industry-standard electrical signal-

ing system. This signaling system can run at very high speeds over inexpensive

copper wires using low power.

The LVDS bus on the X7SPA-L motherboard is used to transport video data from

the built-in graphics adapter to a computer monitor, such as a user-supplied external

LCD display. This motherboard's 18-bpp LVDS connector (6 bits/color) is located

on J5 and the inverter connector for the LCD/back light control is located on J6. It

is possible for certain types of 24-bpp LCD panels (8 bits/color) to be connected to

the 18-bpp interface. Please refer to the following illustration:

Differential Clock

Pair A

Differential Data

Pair A0

Differential Data

Pair A1

Differential Data

Pair A2

18-bpp Connector

Differential Clock

Pair B

Differential Data

Pair B0

Differential Data

Pair B1

Differential Data

Pair B2

Differential Clock

Pair A

Differential Data

Pair A0

Differential Data

Pair A1

Differential Data

Pair A2

Differential Clock

Pair B

Differential Data

Pair B0

Differential Data

Pair B1

Differential Data

Pair B2

Differential Data

Pair A3

Differential Data

Pair B3

24-bpp LVDS Panel

Note: The full 24-bpp range will not be available on the 24-bpp LVDS panel because

the Differential Data Pair A3/B3 is not being driven by the 18-bpp connector. The

LVDS panel will in effect operate as an 18-bpp device. For an in-depth explanation

on this particular subject, go to www.intel.com and search for document 315975.

pdf.