16 drc - dram controller mode register (device #0), 16 drc – dram controller mode register (device #0) – Intel D15343-003 User Manual

Page 85

Register Description

D15343-003

85

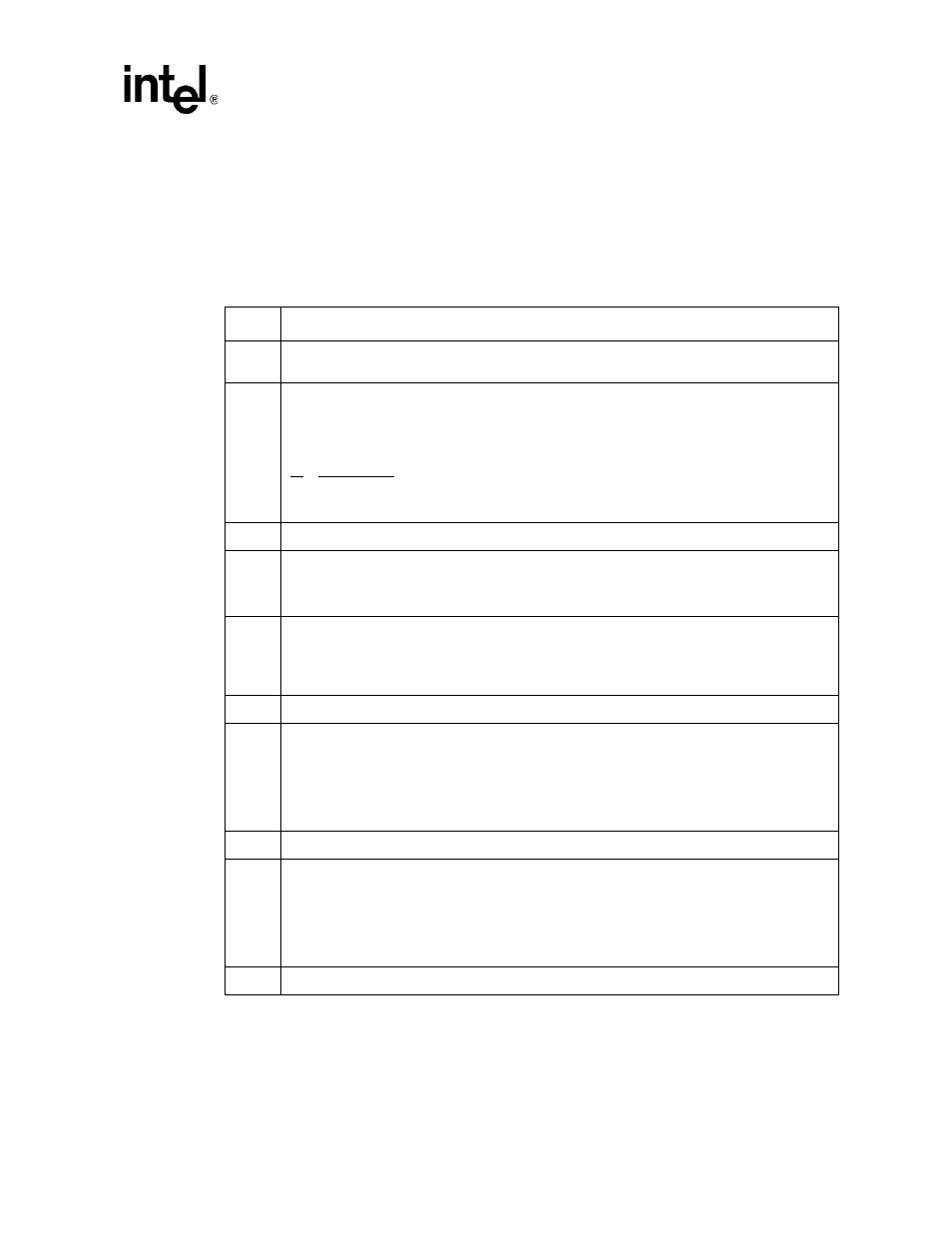

4.9.16

DRC – DRAM Controller Mode Register (Device #0)

Address Offset:

Default Value:

Access:

Size:

70-73h

00000081h

RO, Read/Write

32 bits

Bit

Description

31:30

Revision Number (REV):

Reflects the revision number of the format used for DDR SDRAM

register definition (Read Only).

29

Initialization Complete (IC):

This bit is used for communication of software state between the

Memory Controller and the BIOS. BIOS sets this bit to 1 after initialization of the DDR SDRAM

Memory Array is complete. Setting this bit to a 1 enables DDR SDRAM Refreshes. On power up

and S3 exit, the BIOS initializes the DDR SDRAM array and sets this bit to a 1. This bit works in

combination with the RMS bits in controlling Refresh state:

IC

Refresh State

0 OFF

1 ON

28:24

Reserved

23:22

Number of Channels (CHAN):

Reflects that GMCH supports only one system memory channel.

00: One channel is populated appropriately

Others: Reserved

21:20

DDIM DDR SDRAM Data Integrity Mode

:

00: ECC is not supported on this system. Thus, no read-merge-write on partial writes. ECC data

sense-amps are disabled and the data output is tristate (Default).

XX: Reserved

19:16

Reserved

15

RAS Lock-Out Enable:

Set to a 1 if all populated rows support RAS Lock-Out. Defaults to 0.

If this bit is set to a 1 the DDR SDRAM Controller assumes that the DDR SDRAM guarantees

tRAS min before an auto precharge (AP) completes (Note: An AP is sent with a Read or a Write

command). Also, the DDR SDRAM Controller does not issue an activate command to the auto pre-

charged bank for tRP.

If this bit is set to a 0 the DDR SDRAM Controller does not schedule an AP if tRAS min is not met.

14:13

Reserved

12

Address Tri-state enable (ADRTRIEN):

When set to a 1, the SDRAM Controller will tri-state the

MA, CMD, and CS# (only when all CKEs are deasserted). Note that when CKE to a row is

deasserted, fast chip select assertion is not permitted by the hardware. CKEs deassert based on

Idle Timer and/or max row count control.

0: Address Tri-state Disabled

1: Address Tri-state Enabled

11:10

Reserved