Intel D15343-003 User Manual

Page 72

Intel

®

82854 Graphics Memory Controller Hub (GMCH)

72

D15343-003

4.9

Intel 854 GMCH Main Memory Control, Memory I/O Control

Registers (Device #0, Function #1)

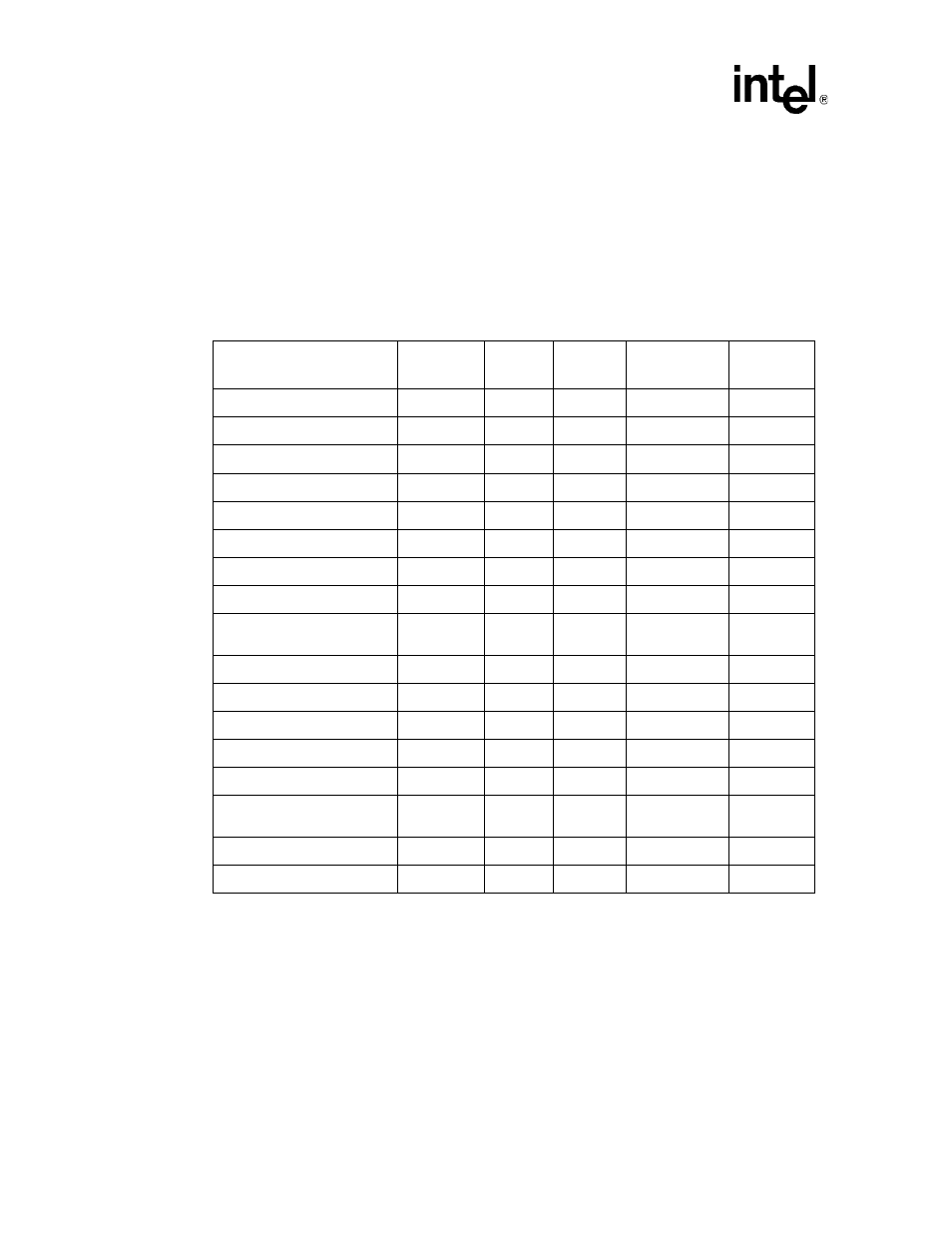

The following table shows the GMCH Configuration Space for Device #0, Function #1. See

“Nomenclature for Access Attributes” on page 42

for access nomenclature.

Table 22.

Host-Hub I/F Bridge/System Memory Controller Configuration Space (Device #0,

Function#1)

Register Name

Register

Symbol

Register

Start

Register

End

Default Value

Access

Vendor Identification

VID

00

01

8086h

RO

Device Identification

DID

02

03

358Ch

RO

PCI Command

PCICMD

04

05

0006h

RO,R/W

PCI Status

PCISTS

06

07

0080h

RO,R/WC

Revision Identification

RID

08

08

02h

RO

Sub-Class Code

SUBC

0A

0A

80h

RO

Base Class Code

BCC

0B

0B

08h

RO

Header Type

HDR

0E

0E

80h

RO

Subsystem Vendor

Identification

SVID

2C

2D

0000h

R/WO

Subsystem Identification

SID

2E

2F

0000h

R/WO

Capabilities Pointer

CAPPTR

34

34

00h

RO

DRAM Row 0-3 Boundary

DRB

40

43

00000000h

RW

DRAM Row 0-3 Attribute

DRA

50

51

7777h

RW

DRAM Timing

DRT

60

63

18004425h

RW

DRAM Controller Power

Management Control

PWRMG

68

6B

00000000h

R/W

Dram Controller Mode

DRC

70

73

00000081h

R/W

DRAM Throttle Control

DTC

A0

A3

00000000h

R/W/L