Advanced chipset features, 4 advanced chipset features -18, 4 advanced chipset features – Intel AW8D User Manual

Page 52

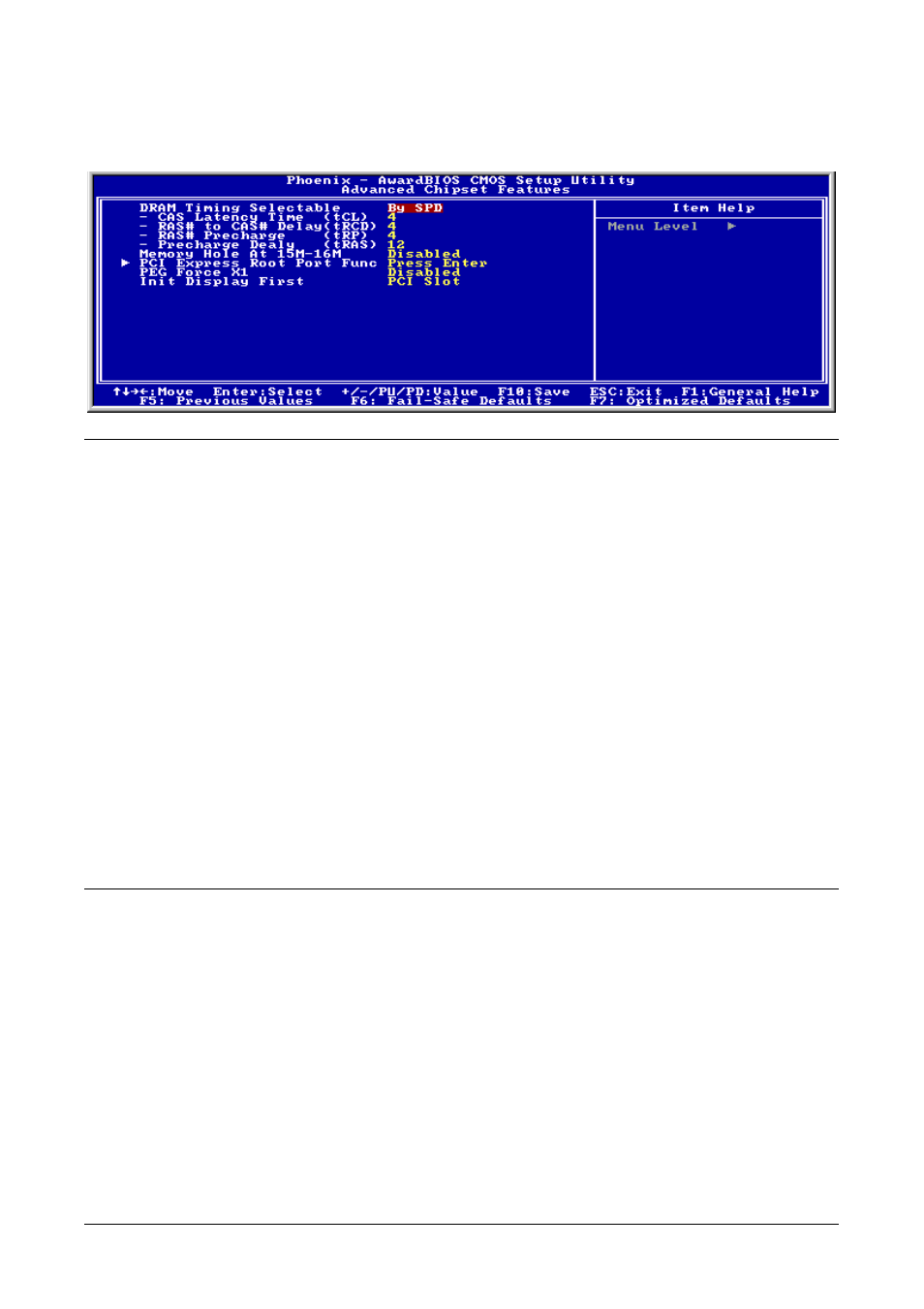

3.4 Advanced Chipset Features

DRAM Timing Selectable

This item sets the optimal timings for the following four items, depending on the memory

module you are using. The default setting “By SPD” configures these four items by reading the

contents in the SPD (Serial Presence Detect) device. The EEPROM on the memory module

stores critical parameter information about the module, such as memory type, size, speed,

voltage interface, and module banks.

-

CAS Latency Time (tCL)

This item controls the latency between the DRAM read command and the time that the data

becomes actually available.

-

RAS# to CAS# Delay (tRCD)

This item controls the latency between the DRAM active command and the read/write

command.

-

RAS# Precharge (tRP)

This item controls the idle clocks after issuing a precharge command to the DRAM.

-

Precharge Delay (tRAS)

This item controls the number of DRAM clocks used for the DRAM parameters.

Memory Hole At 15M-16M

When set to [Enabled], the memory address space at 15M-16M will be reserved for ISA

expansion cards that specifically requires this setting. This makes the memory from 15MB and

up unavailable to the system. Leave this item to its default setting.

3-18

AW8D