5 vertical growth and scalability, Rio-2 interconnect, Ds8000 series: concepts and architecture – IBM DS8000 User Manual

Page 286

264

DS8000 Series: Concepts and Architecture

switch has two ports to connect to the next switch pair with 16 DDMs when vertically growing

within a DS8000. As outlined before, this dual two logical loop approach allows for multiple

concurrent I/O operations to individual DDMs or sets of DDMs and minimizes arbitration

through the DDM/switch port mini loop communication.

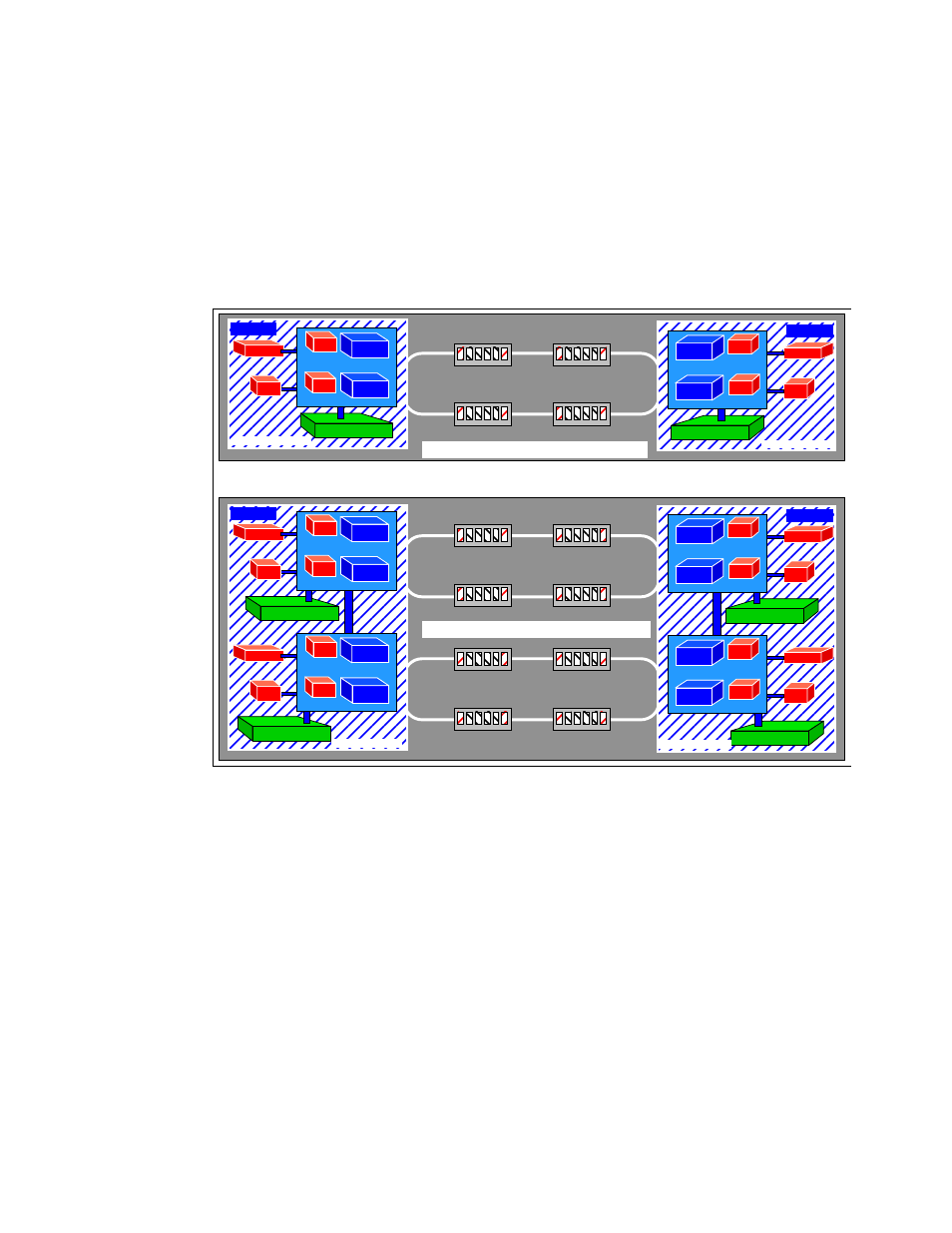

12.3.5 Vertical growth and scalability

Figure 12-9 shows a simplified view of the basic DS8000 structure and how it accounts for

scalability.

Figure 12-9 DS8100 to DS8300 - scale performance linearly - view without disk subsystems

Although Figure 12-9 does not display the back-end part, it can be derived from the number

of I/O enclosures, which suggests that the disk subsystem also doubles, as does everything

else, when switching from a DS8100 to an DS8300. Doubling the number of processors and

I/O enclosures accounts also for doubling the performance or even more.

Again note here that a virtualization layer on top of this physical layout contributes to

additional performance potential.

12.4 Performance and sizing considerations for open systems

To determine the most optimal DS8000 layout, the I/O performance requirements of the

different servers and applications should be defined up front since they will play a large part in

dictating both the physical and logical configuration of the disk subsystem. Prior to designing

the disk subsystem, the disk space requirements of the application should be well

understood.

RIO-2 Interconnect

RIO-2 Interconnect

RIO-2 Interconnect

I/O enclosure

I/O enclosure

I/O enclosure

I/O enclosure

Dual two-way processor complex

Dual four-way processor complex

Fibre Channel switched disk subsystems are not shown

RIO-G Module

POWER5 4-way SMP

RIO-G Module

Memory

L3

L3

Memory

Memory

Processor

Processor

L1,2

Memory

L1,2

Memory

Memory

L3

L3

Memory

Memory

Processor

Processor

L1,2

Memory

L1,2

Memory

Server 1

RIO-G Module

POWER5 4-way SMP

RIO-G Module

Memory

L3

Memory

Processor

Processor

L1,2

Memory

L1,2

Memory

Memory

L3

Memory

Processor

Processor

L1,2

Memory

L1,2

Memory

Server 0

RIO-G Module

POWER5 2-way SMP

Memory

L3

L3

Memory

Memory

Processor

Processor

L1,2

Memory

L1,2

Memory

Server 1

RIO-G Module

POWER5 2-way SMP

Memory

L3

Memory

Processor

Processor

L1,2

Memory

L1,2

Memory

Server 0