Processor bus memory map, Default processor memory map, Processor bus memory map -2 – Motorola MVME2400 User Manual

Page 80: Default processor memory map -2

4-2

Computer Group Literature Center Web Site

Programming the MVME240x

4

Processor Bus Memory Map

The processor memory map configuration is under the control of the PHB

and SMC portions of the Hawk ASIC. The Hawk adjusts system mapping

to suit a given application via programmable map decoder registers. At

system power-up or reset, a default processor memory map takes over.

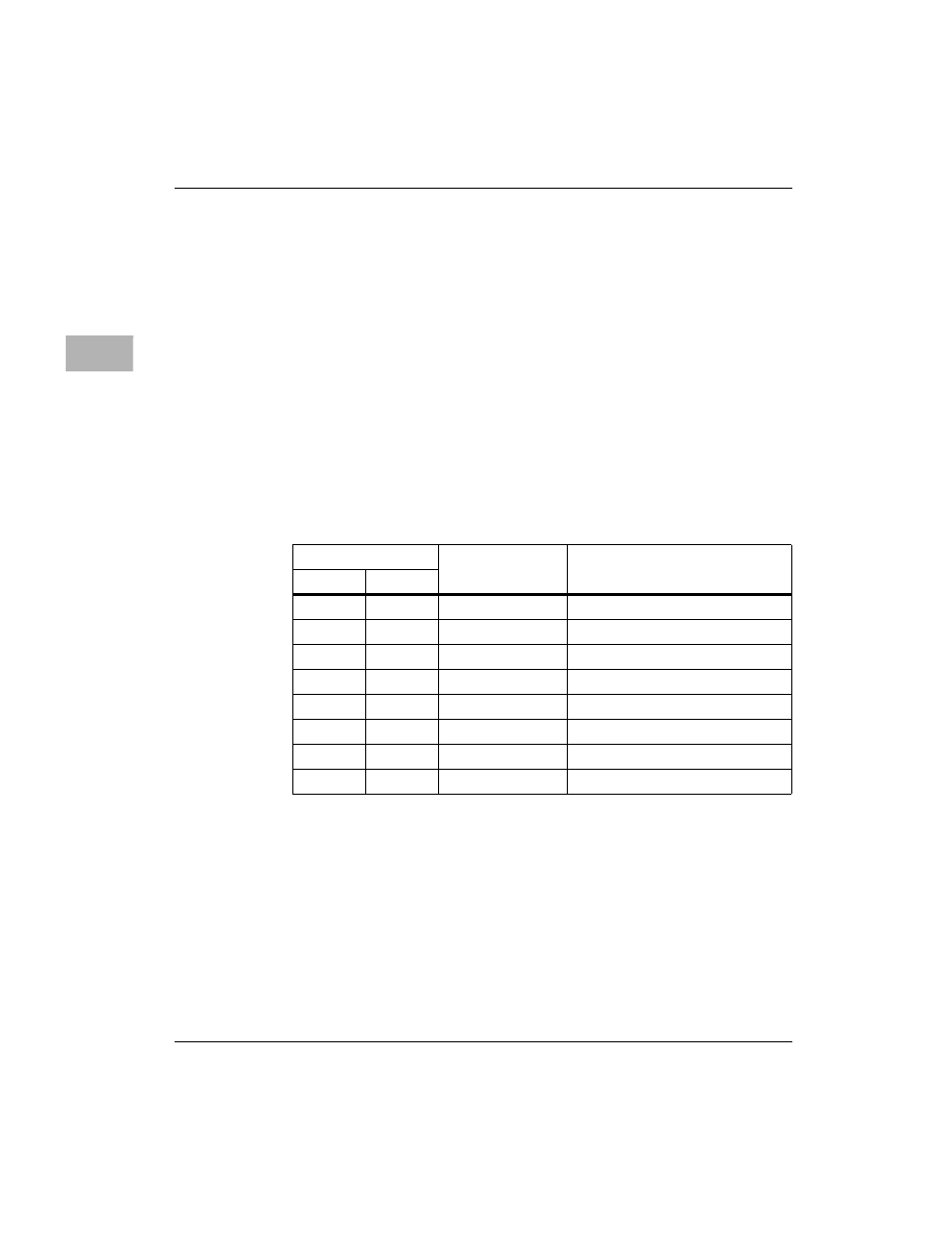

Default Processor Memory Map

The default processor memory map that is valid at power-up or reset

remains in effect until reprogrammed for specific applications.

defines the entire default map ($00000000 to $FFFFFFFF).

Notes

The first 1MB of Flash bank A (soldered Flash up to 8MB)

appears in this range after a reset if the rom_b_rv control bit

in the SMC’s ROM B Base/Size register is cleared. If the

rom_b_rv control bit is set, this address range maps to Flash

bank B (socketed 1MB Flash).

Table 4-1. Processor Default View of the Memory Map

Processor Address

Size

Definition

Start

End

00000000

7FFFFFFF

2GB

Not Mapped

80000000

8001FFFF

128KB

PCI/ISA I/O Space

80020000

FEF7FFFF

2GB-16MB-640KB

Not Mapped

FEF80000

FEF8FFFF

64KB

SMC Registers

FEF90000

FEFEFFFF

384KB

Not Mapped

FEFF0000

FEFFFFFF

64KB

PHB Registers

FF000000

FFEFFFFF

15MB

Not Mapped

FFF00000

FFFFFFFF

1MB

Flash Bank A or Bank B (See Note)