5 timing rule – FUJITSU MCJ3230SS User Manual

Page 120

Host Interface

4-46

C156-E224-01EN

4.5 Timing Rule

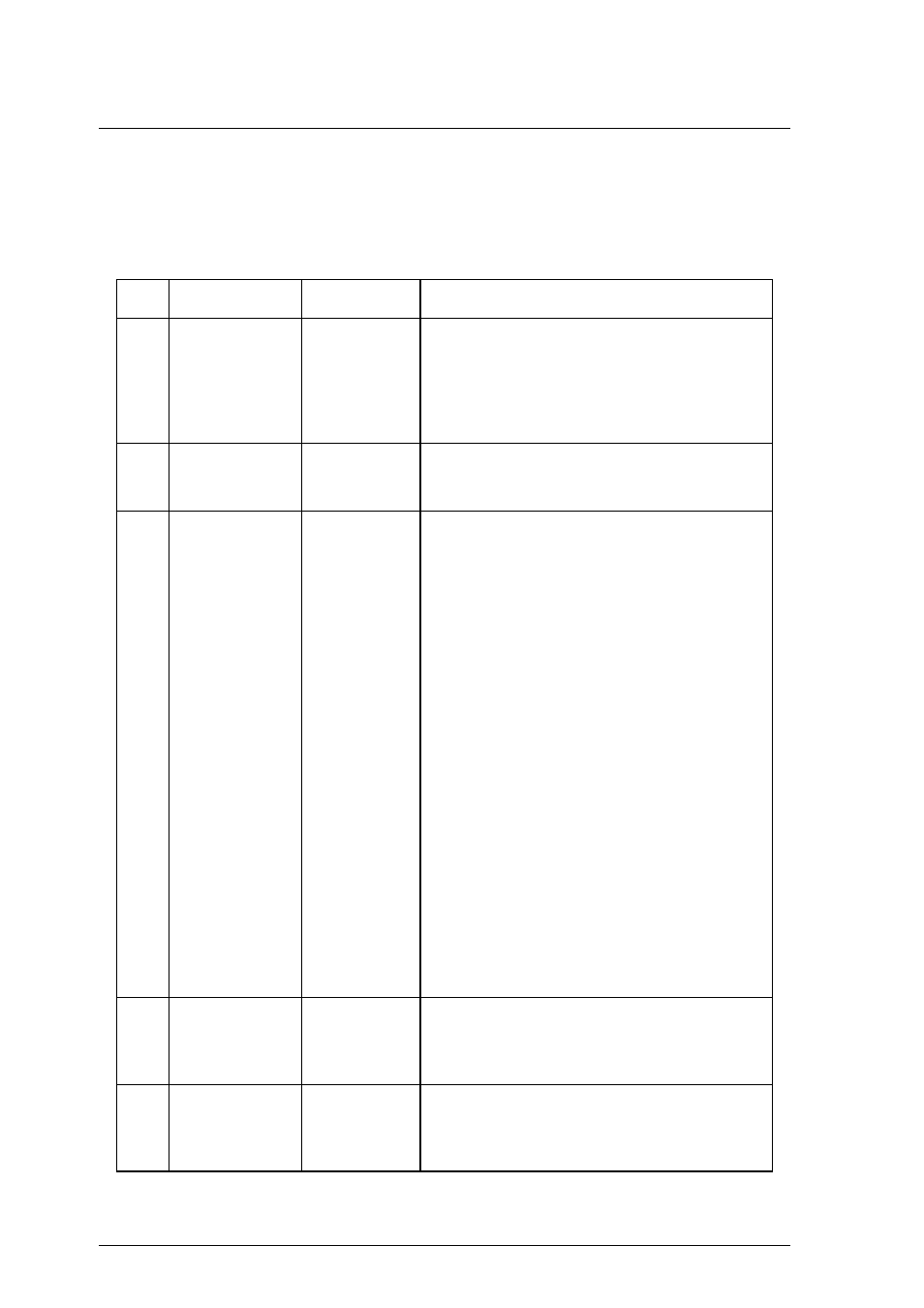

Table 4.75 Timing specifications (1 of 3)

No.

Name

Standard

Timing specification

1

Arbitration

Delay

2.4 µs min.

The minimum wait period between the time the

SCSI device sends a BSY signal and the time the

value on the data bus for determining the

priority of bus use is judged in the

ARBITRATION phase. A maximum time is not

defined.

2

Assertion Period

90 ns min.

Minimum pulse width of an ACK signal sent by

INIT and an REQ signal sent by TARG for

synchronous data transfer.

3

Bus Clear Delay

800 ns max.

Maximum allowable period between the time

either of the following events occurs and the

time the SCSI device stops driving all bus

signals.

(1) Detection of the BUS FREE phase (when

both BSY and SEL signal become false

during Bus Settle Delay).

Note:

Maximum allowable period between

the time both BSY and SEL signal

became false and the time the bus is

released is 1,200 ns.

An SCSI device that requires a period

longer than Bus Settle Delay for the

detection of the BUS FREE phase

must release the bus within (Bus Clear

Delay) minus (Bus Settle Delay excess

time).

(2) Another SCSI device asserts the SEL signal

during an ARBITRATION phase.

(3) The RST signal becomes true (RESET

condition).

4

Bus Free Delay

800 ns min.

Minimum wait period between the time the

SCSI device detects a BUS FREE phase and the

time it sends a BSY signal to initiate an

ARBITRATION phase.

5

Bus Set Delay

1.8 µs max.

Maximum allowable period between the time an

SCSI device detects a BUS FREE phase and the

time it sends BSY and SCSI ID signals to

initiate an ARBITRATION phase.