Cache memory – HP Vectra 500 Series User Manual

Page 73

73

3 System Board (P/Ns D3657-63001 and D3661-63001)

Devices on the Processor Local Bus

The computer will execute erratically, if at all, if the configuration switches

are set to operate at a higher processor speed than the processor is capable

of supporting. This may cause damage to the PC.

Setting the switches to operate at a slower speed than the processor is

capable of supporting would not cause any failure of operation but would

cause instructions to be executed more slowly than they should be.

Cache Memory

The PC allows for the provision of two levels of cache memory:

•

Level-one cache memory which is fabricated by Intel in the Pentium

processor chip

•

Level-two cache memory is optionally installed as a memory module on

the system board

Each acts as temporary storage for data and instructions from the main

memory. Since the system is likely to use the same data several times, it is

faster to get it from the on-chip level-one cache than from the main memory.

The level-two cache memory, when fitted, has a 32-byte line size (a line is an

area of memory of a fixed size). It is controlled by the PL/PCI bridge chip

(SB82437FX). A single HP cache memory module consists of 256 KB of

direct mapped, synchronous or asynchronous, static random access memory

(SRAM). The synchronous cache memory module achieves 10% better

performance than the asynchronous module.

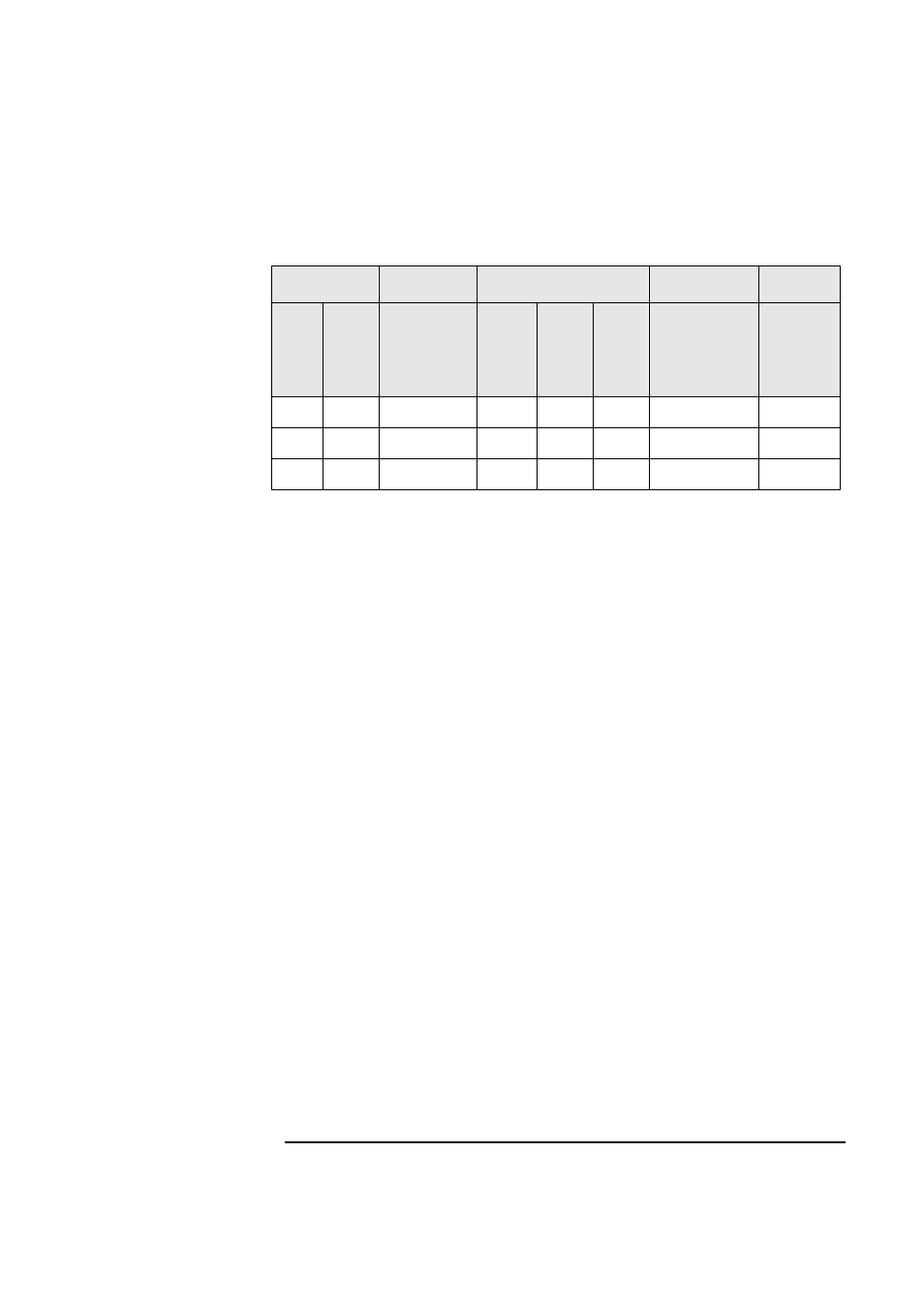

1

2

Processor-

Local Bus

Frequency

3

4

7

Frequency

Ratio

(Processor:

Local Bus)

Processor

Frequency

Open

Closed

66 MHz

Closed

Closed

Closed

2.5

166 MHz

Closed

Open

60 MHz

Open

Closed

Closed

3.0

180 MHz

Open

Closed

66 MHz

Open

Closed

Closed

3.0

200 MHz

Switch

Switch