Pci, cache and memory controller (sb82437fx-66), Sb82437fx-66 feature summary – HP Vectra 500 Series User Manual

Page 63

63

3 System Board (P/Ns D3657-63001 and D3661-63001)

Principal Components and Features

PCI, Cache and Memory Controller (SB82437FX-66)

The SB82437FX-66 device integrates cache and memory control functions

and provides bus control functions for the transfer of information between

the microprocessor, cache, main memory and the PCI bus. The cache

controller supports the Pentium Cache Write-Back mode and 256 KB of

direct mapped, write-back level-two cache, using synchronous pipeline

burst SRAMs.

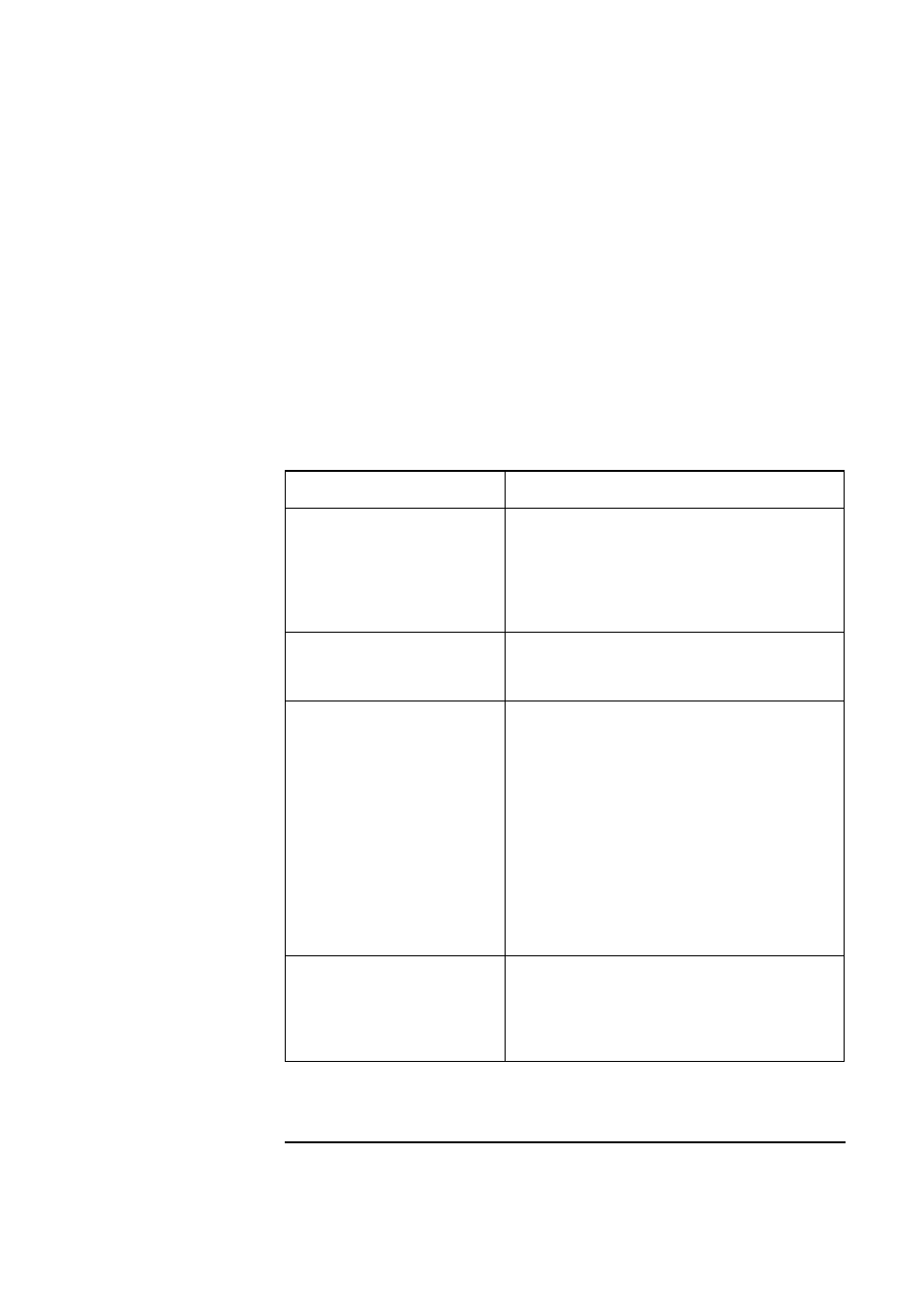

SB82437FX-66 Feature Summary

Function

Features

Cache controller

❒ Direct mapped organization

❒ Buffered write-back

❒ External cache tags

❒ 32-byte line size

❒ Uses synchronous pipeline burst SRAM

❒ Supports 3-1-1-1

1

burst reads

Write buffer

❒ Buffers all processor writes to main memory

❒ Buffers memory writes to PCI for selected memory regions

❒ Supports 3-1-1-1

1

write access timing

DRAM controller

❒ Uses dedicated DRAM memory address and data buses

❒ Page mode - one or two pages open simultaneously

❒ Supports pipelined accesses

❒ Full RAS/CAS programmability

❒ Flexible bank configurations (each bank programmable for

DRAM size, bank width and single or double-sided modules)

❒ Self configuring bank start addresses

❒ Shadow RAM support for the memory region 640 KB - 1 MB

(in 16-KB segments)

❒ System management memory support

❒ RAS only refresh

❒ Fast memory access 7-2-2-2

1

with Extended Data Out (EDO)

memory

PCI slave interface

❒ Becomes processor (local) bus master to generate DRAM

requests on behalf of other PCI bus masters

❒ Supports PCI bus burst cycles

❒ Supports posted writes to DRAM for PCI burst writes

❒ Supports read-ahead from DRAM for PCI burst reads