Devices on the processor local bus (d4051-63001), Main memory (uma), Cache memory (d4051-63001) – HP Vectra 500 Series User Manual

Page 44

44

2 System Board - (SiS Chipset) (Part Number: D4051-63001)

Devices on the Processor Local Bus (D4051-63001)

Devices on the Processor Local Bus (D4051-63001)

Main Memory (UMA)

The SiS 5511 chip can support single-sided or double-sided 64/72 bits (with

or without parity) FP (Fast Page mode) or EDO (Extended Data Output)

DRAM (dynamic random-access memory) modules. Half populated banks

are also supported. The PC can use 60 ns EDO or 70 ns FP DRAM.

It is also possible to mix the EDO DRAM and FP DRAM bank by bank and

the corresponding DRAM timing will be switched automatically according to

register setting. Both symmetrical and asymmetrical type DRAMs are

supported.

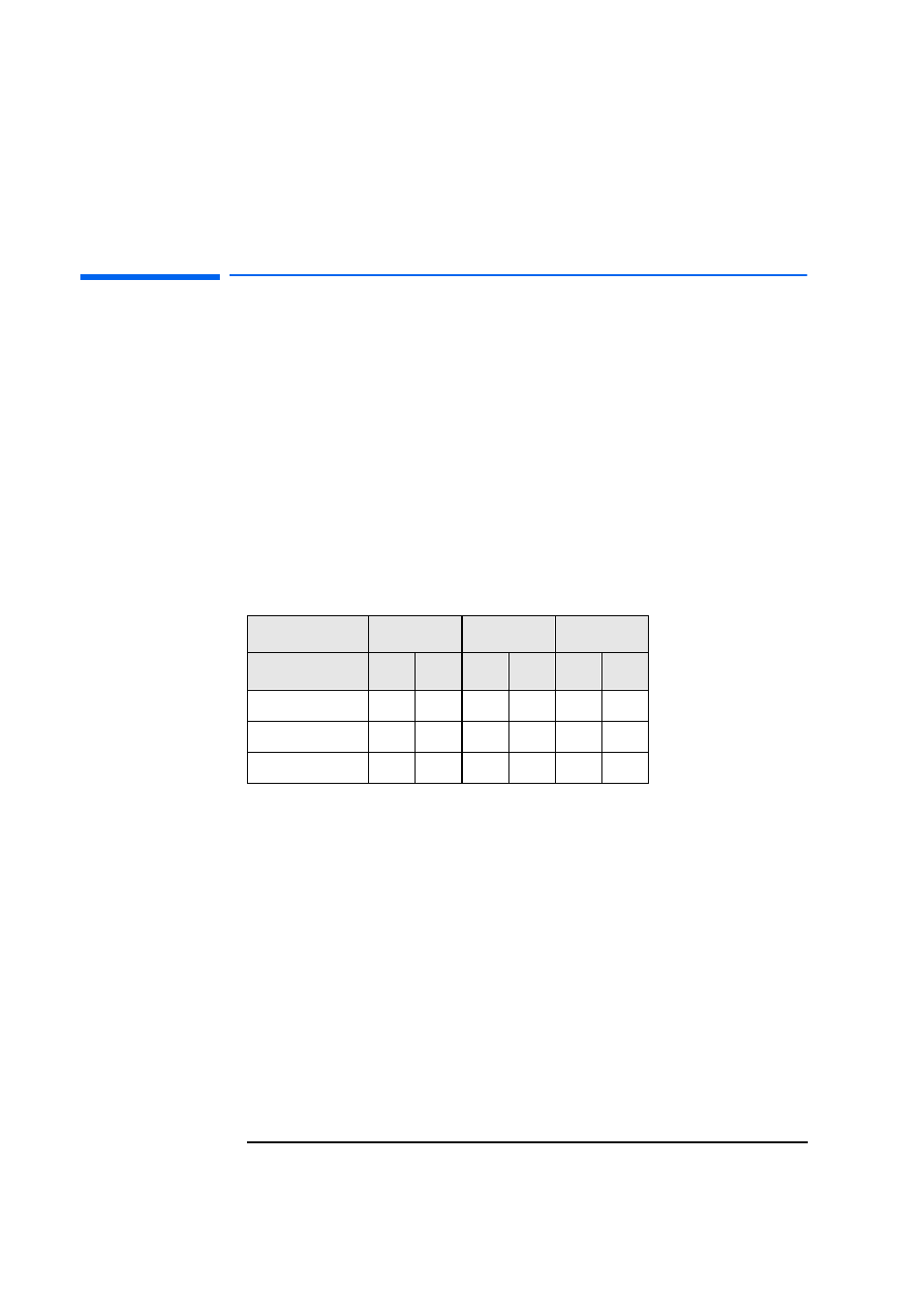

The following table is an example of how to use the memory module banks,

with three different configurations.

Cache Memory (D4051-63001)

The PC supports two levels of cache memory:

•

Level-1 (L1), cache memory which is incorporated within the Pentium

processor chip.

•

Level-2 (L2), cache memory which is optionally installed as a memory

module on the system board.

Cache memory acts as temporary storage for data and instructions from

main memory. Since the system is likely to use the same data several times,

it is faster to get it from the on-chip cache than from the main memory.

BANK A

BANK B

BANK C

Memory Total

A1

A2

B1

B2

C1

C2

8 MB

4 MB

4 MB

12 MB

4 MB

4 MB

4MB

16 MB

8 MB

8 MB