Feature summary – HP Vectra 500 Series User Manual

Page 35

35

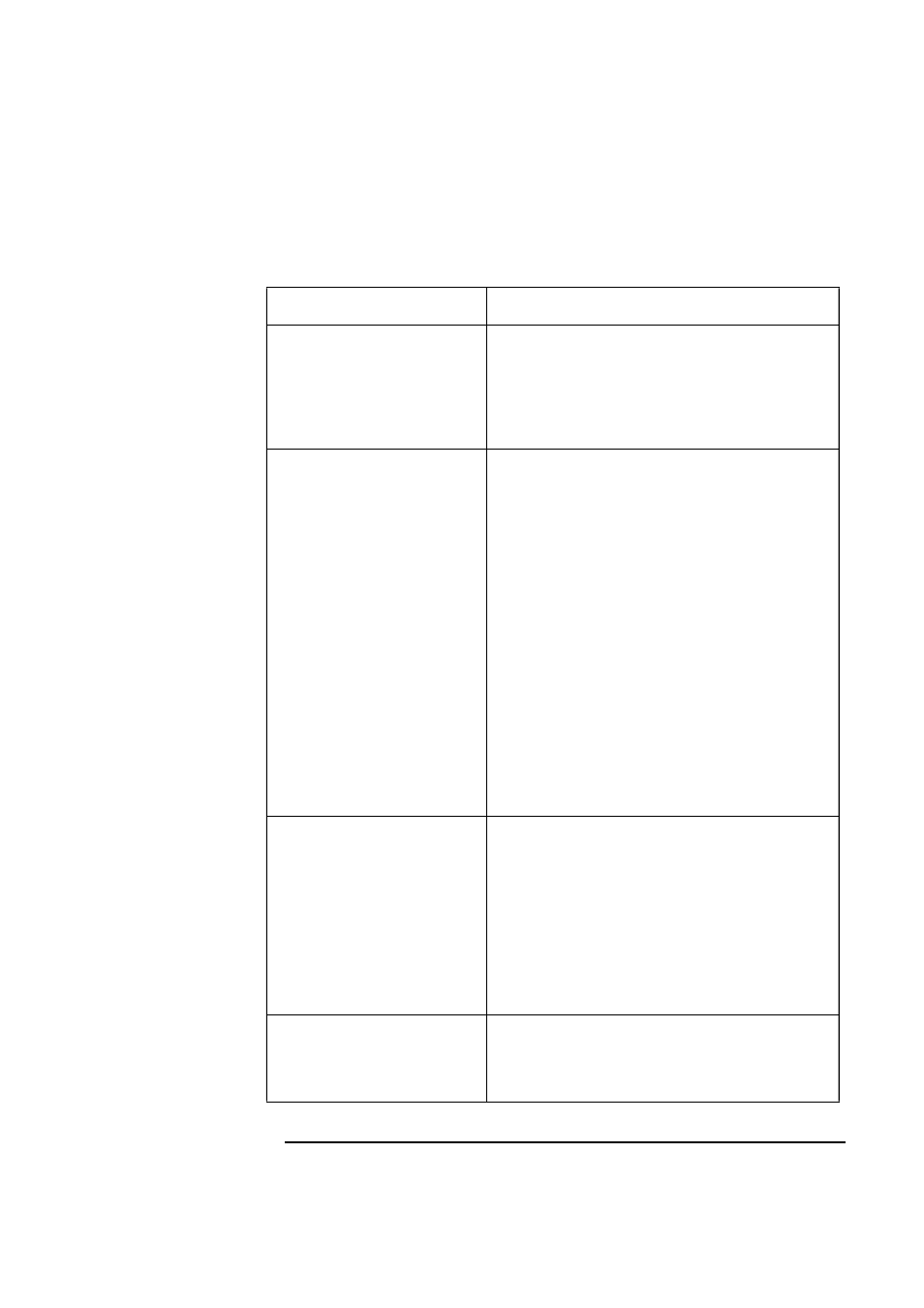

2 System Board - (SiS Chipset) (Part Number: D4051-63001)

SiS Chipset

Feature Summary

Function

Features

Cache controller

❒ 8 bits or 7 bits TAG with Direct mapped organization.

❒ Write back mode (only supported by BIOS)

❒ Uses burst and pipelined burst SRAMs.

❒ 64-KByte to 1 MByte cache summary

❒ Read/Write cycle of 3-1-1-1 using burst or pipelined SRAMS at

66 MHz.

Integrated DRAM controller

❒ Supports four banks of SIMMs.

❒ Supports 256K, 512K, 1MB, 2MB, 4MB, 16MB 70ns FP/EDO

DRAM.

❒ Supports 4K refresh DRAM.

❒ Supports 3V or 5V DRAM.

❒ Supports symmetrical and asymmetrical DRAM.

❒ Supports 32 bits/64 bits mixed mode configuration.

❒ Supports concurrent write back.

❒ Supports Read Cycle Power Saving Mode.

❒ Table-free DRAM configuration, auto-detect DRAM size, bank

density, single/double sided DRAM, EDO/FP DRAM for each

bank.

❒ Supports CAS before RAS “Intelligent Refresh”.

❒ Supports Relocation of System Management Memory.

❒ Optional Parity Checking.

❒ Programmable CAS# Driving Current.

❒ Fully configurable for the Characteristic of Shadow RAM (640

KByte to 1 Mbyte).

❒ Supports EDO/FP 5/6-2-2-2/-3-3-3 burst read cycles.

Integrated PCI Bridge

❒ Supports asynchronous PCI clock.

❒ Translates the CPU cycles into the PCI bus cycles.

❒ Provides CPU-to-PCI Read Assembly and Write Disassembly

Mechanism.

❒ Translates sequential CPU-to-PCI Memory Write Cycles into PCI

Burst Cycles.

❒ Zero Wait State Burst Cycles.

❒ Provides a prefetch mechanism dedicated for IDE Read.

❒ Supports Advanced Snooping for PCI Master Bursting.

❒ Maximum PCI burst transfer from 256 bytes to 4 Kbytes.

PCI bus arbiter

❒ Supports PCI bus arbitration for up to four masters.

❒ Supports rotating priority mechanism.

❒ Hidden arbitration scheme minimizes arbitration overhead.

❒ Supports concurrence between CPU to memory and PCI to PCI.