Registers definition, Control register (0x4), Address register low order 16-bits (0x5) – Sundance SMT351 User Manual

Page 19: Address register high order 16-bits (0x6), Count register low order 16-bits (0x7)

Registers definition

The SMT351 is configured via a set of 16-bits registers described in this section.

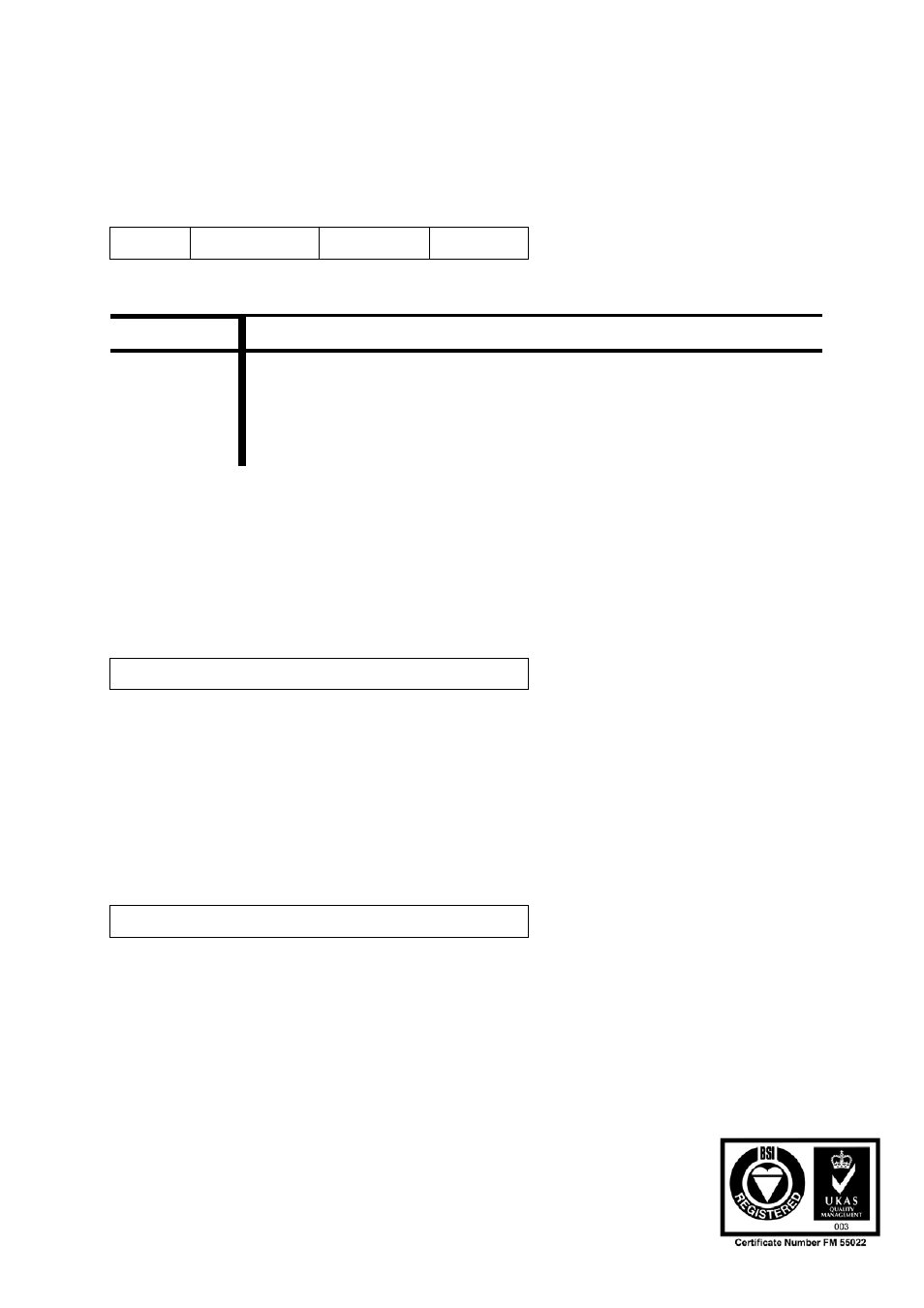

Control register (0x4)

15-3 2

1 0

- RST_INPUT

RDBKEN

START

-

R/W,0 R/W,0

R/W,0

Field

Description (flags are active when 1)

START

Writing ‘1’ and then ‘0’ to this bit will start the storage of the data.

RDBKEN

Read back enable. When this bit is set read back of memory is

enabled and SMT351 starts outputting data.

RST_INPUT

When this bit is set to 1, the data are cleared from the input buffer.

Address register Low order 16-bits (0x5)

Write in this register the low 16-bits of address at which you want to start the cycle.

15-0

Low order 16-bits of the address

R/W,0

Address register High order 16-bits (0x6)

Write in this register the high 16-bits of address at which you want to start the cycle.

15-0

High order 16-bits of the address

R/W,0

Count register Low order 16-bits (0x7)

Write in this register the low 16-bits of total number of 32-bits words you want to

store.